#### Universitat de Valéncia Escuela Técnica Superior de Ingeniería Programa de Doctorado en Ingeniería Electrónica

# TESIS DOCTORAL Spiking Neural Networks models targeted for implementation on Reconfigurable Hardware.

Autor: Taras Iakymchuk Director: Alfredo Rosado Muñoz

${\rm Mayo}\ 2017$

#### Declaration of Authorship

I, Taras Iakymchuk, declare that this thesis titled, 'Spiking Neural Networks models targeted for implementation on Reconfigurable Hardware' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| oigned: |  |  |

|---------|--|--|

|         |  |  |

|         |  |  |

| _       |  |  |

| Date:   |  |  |

|         |  |  |

#### UNIVERSITY OF VALENCIA

#### Abstract

Departamento de Ingeniería Electrónica Escuela Téchnica Superior de Ingeniería

#### Doctor of Philosophy

#### Spiking Neural Networks models targeted for implementation on Reconfigurable Hardware.

by

This thesis describes a novel architecture of the Spiking Neural Networks implemented in hardware using Field-Programmable Gate Arrays. By starting from the state of the art theoretical and practical works, a new approach to the problem is proposed. The presented work is dealing with both software and hardware topics such as:

- Spiking neural models with focus on their performance and feasibility in hardware.

A novel simplified neuron model is created and tested.

- Learning of SNNs in software and hardware. The well-known learning algorithms are implemented and tested with the simplified neuron model.

- Data representation and conversion in spiking neural systems. A new version of Address-Event Representation protocol is proposed, effectively allowing the finite automata approach to the SNN implementation. A novel hardware architecture to encode images is presented.

- Hardware platforms' resources and their usability for SNN implementation. The latest commercial FPGA devices are evaluated as the prospective platform for large-scale SNN implementation.

- Spiking perceptron and spiking Restricted Boltzmann machine implementation.

Two popular network models are implemented and tested, utilizing the proposed neuronal model.

- Neural network learning in hardware. The previously studied algorithms are implemented in the hardware.

The aforementioned material was partially published in two journal and five conference papers. The system has been fully developed and tested using public domain datasets.

*Contents* iv

### Acknowledgements

This thesis would be never finished without many people, helping me on my journey. I owe all of you.

I am very grateful to prof. Bernabé Linares-Barranco and prof. Giacomo Indiveri for inviting me to visit their fantastic insitutions.

The guy from UV who was making a seminar about ELMs in 2014. I don't remember your name but while trying to solve your problem I came to a vectored architecture. If you read this, thank you!

Karolina Zuniga gave me motivation to finish this work when I was ready to give up.

I will be forever indebted to Alfredo, for taking me into this wonderful journey and patience to my horrible bureaucratic paperwork skills.

My parents and my sister, thank you for your support and understanding. I know, it took me quite a time.

# Contents

| D            | eclar  | tion of Authorship                       | ii  |

|--------------|--------|------------------------------------------|-----|

| A            | bstra  | ${f t}$                                  | ii  |

| A            | ckno   | ledgements                               | iii |

| Li           | ist of | Figures                                  | vii |

| Li           | ist of | Tables x                                 | iii |

| A            | bbre   | ations                                   | хv  |

| $\mathbf{R}$ | esum   | n de la tesis doctoral                   | 1   |

|              | 0.1    | Capítulo 2                               | 4   |

|              | 0.2    | Capítulo 3                               | 5   |

|              | 0.3    | Capítulo 4                               | 5   |

|              | 0.4    | Capítulo 5                               | 6   |

|              | 0.5    | Capítulo 6                               | 8   |

|              | 0.6    | Capítulo 7                               | 8   |

| 1            | Intr   | duction                                  | 9   |

|              | 1.1    | Goals and aims of this thesis            | 9   |

|              | 1.2    |                                          | 10  |

| 2            | Net    | al networks and models: a brief overview | 13  |

|              | 2.1    | Biological neurons and neural models     | 14  |

|              | 2.2    | Neural plasticity                        | 17  |

|              | 2.3    | Neural models                            | 18  |

|              |        | 2.3.1 Biological spiking neuron          | 19  |

|              |        | 2.3.2 Hodgkin-Huxley Model               | 21  |

|              |        |                                          | 23  |

|              |        | 2.3.4 Simplified Spiking Neural model    | 25  |

|              | 2.4    |                                          | 27  |

|              | 2.5    |                                          | 29  |

|              |        | · ·                                      | 29  |

|              | 2.6    |                                          | 32  |

*Contents* vi

| 3 | Net  | ıral encoding                                                           | <b>35</b> |

|---|------|-------------------------------------------------------------------------|-----------|

|   | 3.1  | Rate-based encoding                                                     | 35        |

|   | 3.2  | Position coding                                                         | 36        |

|   | 3.3  | Visual receptive fields                                                 | 38        |

|   |      | 3.3.1 Receptive field neuron response                                   | 39        |

|   |      | 3.3.2 Gabor filters                                                     | 40        |

|   | 3.4  | Address-Event Representation                                            | 40        |

|   |      | 3.4.1 Variable timeslot length AER (VTSAER)                             | 43        |

|   |      | 3.4.2 Online event encoding into VTSAER                                 | 45        |

| 4 | Eva  | luation of the simplified model                                         | <b>51</b> |

|   | 4.1  | Image encoding                                                          | 51        |

|   | 4.2  | Network architecture                                                    | 53        |

|   | 4.3  | Results                                                                 | 53        |

|   | 4.4  | Evaluation of the RBM based on the simplified model                     | 57        |

| 5 | Spil | king neuron as a finite automaton and its hardware implementation       | 63        |

|   | 5.1  | FPGA in scope of the neuromorphic hardware                              | 63        |

|   |      | 5.1.1 Block RAM                                                         | 64        |

|   |      | 5.1.2 DSP48 block                                                       | 65        |

|   |      | 5.1.3 Fixed-point arithmetic and accuracy in FPGA                       | 66        |

|   | 5.2  | VTSAER as a basis for neuron architecture                               | 67        |

|   |      | 5.2.1 $$ Binary shift-based LIF and multiplication-based LIF neurons $$ | 69        |

|   | 5.3  | STDP on-chip learning for the Automata neuron                           | 70        |

|   | 5.4  | FPGA implementation of the Automata neuron                              | 72        |

|   |      | 5.4.1 Neuron functional blocks description                              | 77        |

|   |      | 5.4.2 Simulation of Automata neuron functioning                         | 81        |

|   | 5.5  | Composing a layer of Automata Neurons. Multi-layered networks           | 82        |

|   | 5.6  | The limitations of the fixed-point models                               | 84        |

|   | 5.7  | Complete neuromorphic data processing system design with the vectored   |           |

|   |      | architecture                                                            | 86        |

| 6 | Rec  | eptive field encoding and spike train generation                        | 89        |

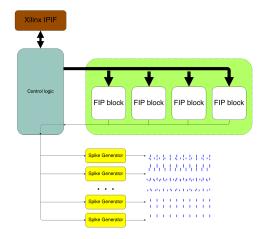

|   | 6.1  | Frobenius inner product calculation implementation                      | 92        |

|   | 6.2  | Hardware occupation and speed of fully parallel FIP implementation      | 93        |

|   | 6.3  | Vectored FIP computation                                                | 94        |

|   | 6.4  | On numerical accuracy of RF computation and spiking response            | 96        |

|   | 6.5  | Comparison of fully parallel and vectored FIP implementation            | 97        |

| 7 | Fin  | al remarks and conclusions                                              | 99        |

|   | 7.1  | Comparison with the state of the art hardware implementations           | 99        |

|   | 7 2  | Conclusions                                                             | 101       |

Bibliography 103

# List of Figures

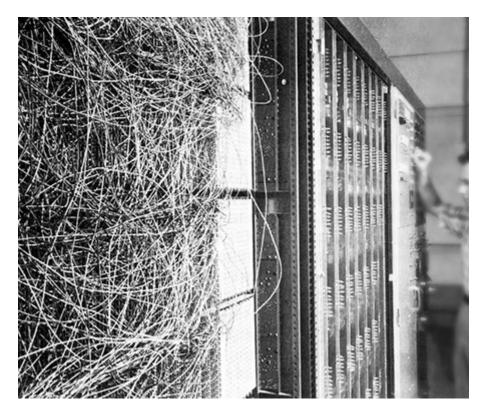

| 2.1  | Mark I perceptron, the first neural network device. Note the amount and complexity of wiring. The connectionist problem (number of connections                                                                                                                                          |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | per node) remains an important issue even now, in 2017                                                                                                                                                                                                                                  | 15 |

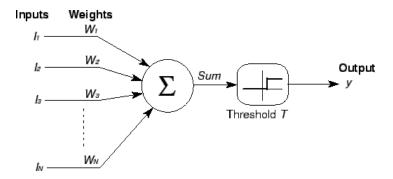

| 2.2  | First generation McCulloch-Pitts perceptron schematic                                                                                                                                                                                                                                   | 15 |

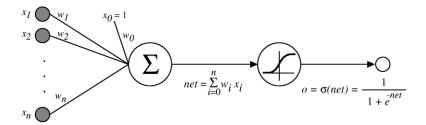

| 2.3  | Sigmoid function neuron schematic. Image courtesy: Tom M. Mitchell.                                                                                                                                                                                                                     |    |

|      | Machine Learning.McGraw Hill. 1997. [7]                                                                                                                                                                                                                                                 | 16 |

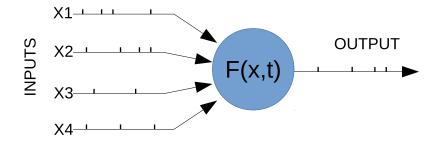

| 2.4  | Spiking neuron model. The output sequence of spikes is computed as a                                                                                                                                                                                                                    |    |

|      | function of input $X$ and time $t$                                                                                                                                                                                                                                                      | 16 |

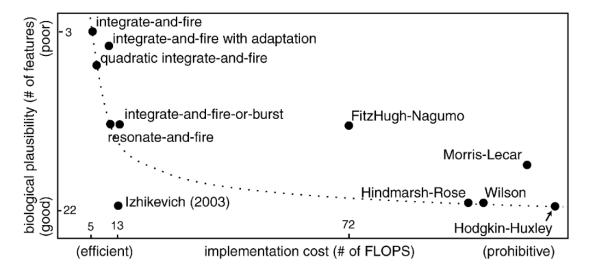

| 2.5  | Plausibility-complexity comparison. FLOPS scale is for digital implementations [14]                                                                                                                                                                                                     | 19 |

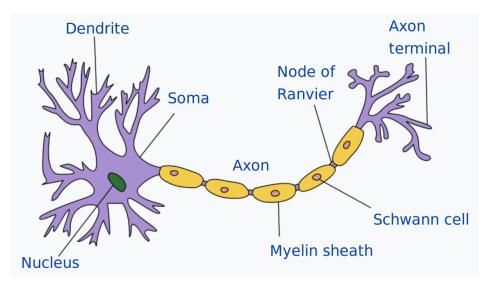

| 2.6  | The most common neuron types and their structure. Image courtesy of [15]                                                                                                                                                                                                                | 20 |

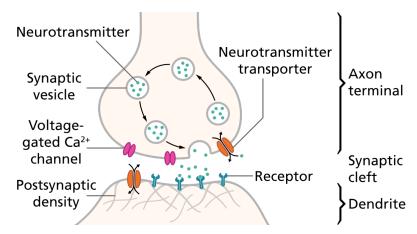

| 2.7  | Biological synapse structure. Image courtesy of [16]                                                                                                                                                                                                                                    | 21 |

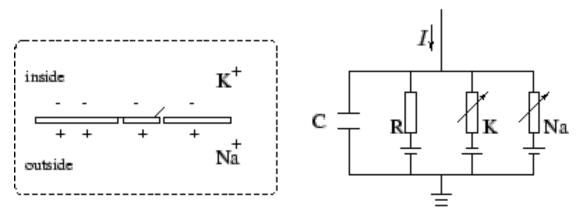

| 2.8  | Hodgkin-Huxley model circuit. Left: simplified synapse membrane schemat-                                                                                                                                                                                                                |    |

|      | ics with K-Na ion distribution. Right: equivalent electric circuit                                                                                                                                                                                                                      | 22 |

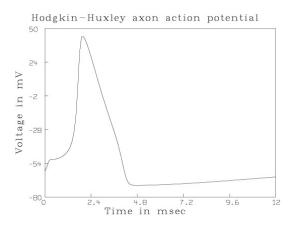

| 2.9  | Hodgkin-Huxley axon action potential vs time in the presence of constant                                                                                                                                                                                                                |    |

|      | stimulus                                                                                                                                                                                                                                                                                | 22 |

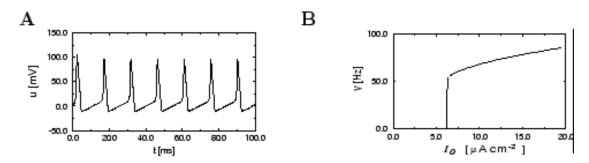

| 2.10 | Hodgkin-Huxley spiking model. A: Sequence of spikes caused by constant                                                                                                                                                                                                                  |    |

|      | stimulation. B: Intensity-frequency plot                                                                                                                                                                                                                                                | 23 |

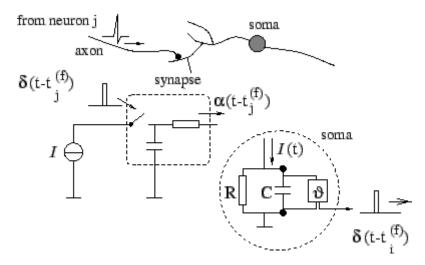

|      | Leaky integrate-and-fire (LIF) model                                                                                                                                                                                                                                                    | 24 |

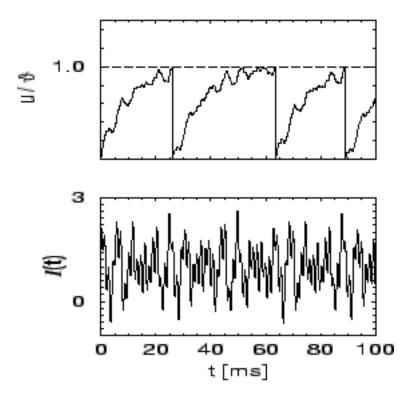

| 2.12 | Leaky integrate-and-fire model dynamics of the neuron driven by irregular current so the membrane positive charge change and leakage can be observed. Injected current is on the bottom plot, membrane potential is on the top plot. When the driving current is negative, the membrane |    |

|      | potential decreases                                                                                                                                                                                                                                                                     | 25 |

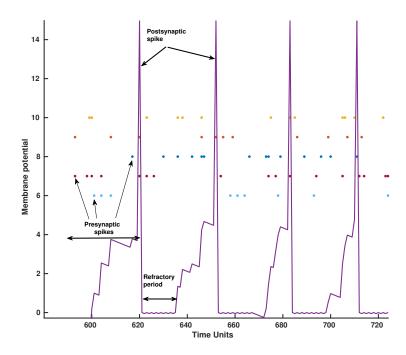

| 2.13 | Membrane potential dynamics of a single neuron with simplified mem-                                                                                                                                                                                                                     |    |

|      | brane model. After several incoming spikes, the membrane potential surpasses threshold and neuron fires a postsynaptic spike. For better visi-                                                                                                                                          |    |

|      | bility, neuron potential is increased three times for one TU after spiking.                                                                                                                                                                                                             |    |

|      | During refractory period, neuron does not change its potential. Presy-                                                                                                                                                                                                                  | 07 |

| 0.14 | naptic spikes are shown with colored dots                                                                                                                                                                                                                                               | 27 |

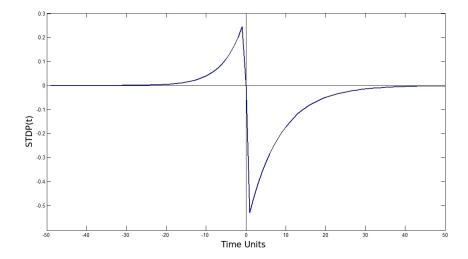

| 2.14 | STDP curve used for learning. This type of curve has stronger depression value than potentiation, increasing specificity. $A^+ = 0.6, A^- = 0.3, \tau^+ =$                                                                                                                              |    |

|      | $8, \tau^- = 5. \dots $                                                                                                                                                           | 29 |

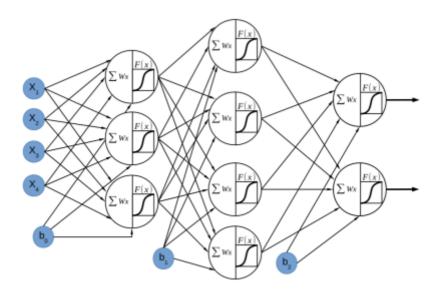

| 2.15 | Multilayer perceptron schematic                                                                                                                                                                                                                                                         | 30 |

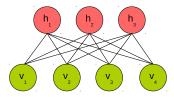

|      | Restricted Boltzmann Machine network.                                                                                                                                                                                                                                                   | 32 |

List of Figures viii

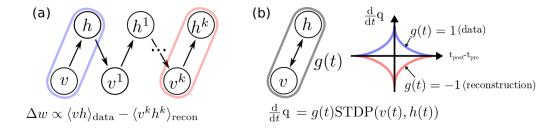

| 2.17 | Event-based CD algorithm. The RBM is unrolled into Monte-Carlo Markov Chain. The correlation between visible and hidden layer causes weight potentiation; the correlation between reconstruction of layers causes depression Source: [31]                                                       | . 33 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

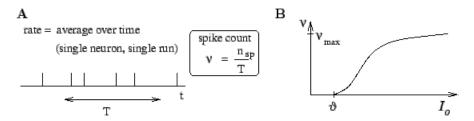

| 3.1  | Rate-based coding of analog stimulus (plot B) into a spike train (plot A). Image source: [13]                                                                                                                                                                                                   | . 36 |

| 3.2  | Average spike density coding of analog stimulus. Image source: [13]                                                                                                                                                                                                                             | . 36 |

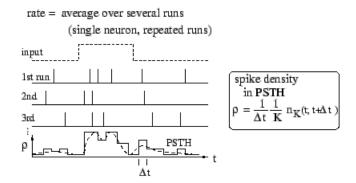

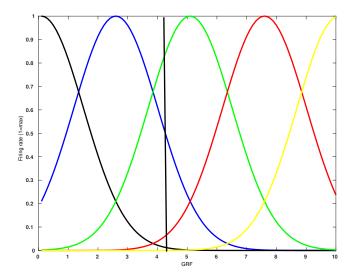

| 3.3  | GRF encoding of the [010] range with 5 fields (5 spike trains). The black vertical line denotes one analog input, and the points of crossing with Gaussian curves give the corresponding spiking frequency normalized in [01] range                                                             | . 37 |

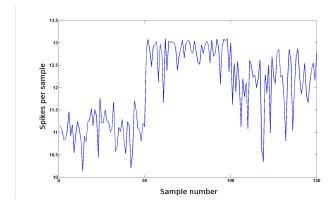

| 3.4  | Average amount of spikes per sample for Iris dataset. First 50 samples are for the <i>Setosa</i> , samples from 51 to 100 are for <i>Versicolor</i> and the last 50 samples are the <i>Virginica</i> species. Note that the variation of the spike density is less than 20% between the classes | . 37 |

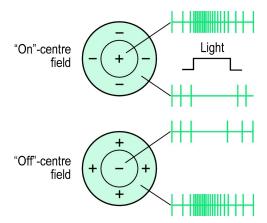

| 3.5  | Off-centered and on-centered neural receptive field and corresponding                                                                                                                                                                                                                           |      |

|      | spike trains. Source: [41]                                                                                                                                                                                                                                                                      |      |

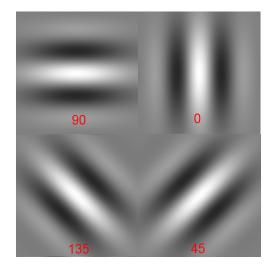

| 3.6  | Different types of Gabor RF                                                                                                                                                                                                                                                                     | . 39 |

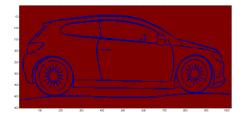

| 3.7  | Sample monochromatic image of a car                                                                                                                                                                                                                                                             | 41   |

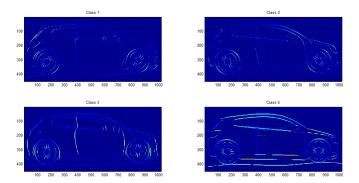

| 3.8  | Sample image, converted with 4 different receptive fields with orientation of $0^{\circ}$ , $45^{\circ}$ , $90^{\circ}$ and $135^{\circ}$                                                                                                                                                       | . 41 |

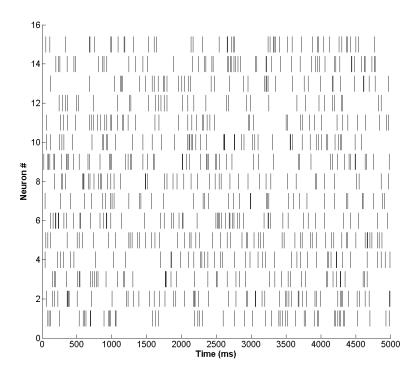

| 3.9  | Sample spike raster plot of 15 neurons spiking over 5000 ms                                                                                                                                                                                                                                     |      |

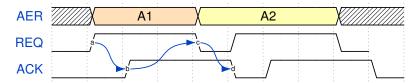

| 3.10 | Asynchronous AER data communication. The transmitter sets the data on the <b>AER</b> bus, raises the request signal <b>REQ</b> high and waits for the acknowledge signal <b>ACK</b> from the receiver. After this, <b>REQ</b> goes low,                                                         |      |

| 3.11 | driving $ACK$ low. The cycle can be repeated                                                                                                                                                                                                                                                    | . 42 |

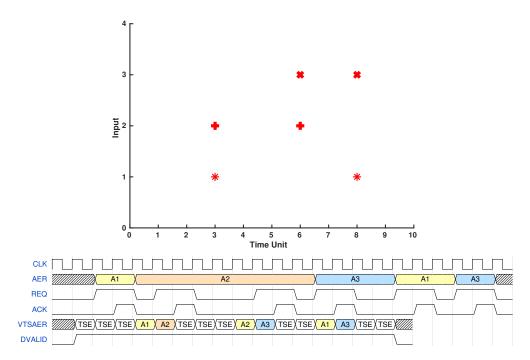

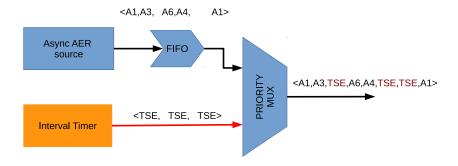

|      | stream is shown from the perspective of the synchronous receiver                                                                                                                                                                                                                                | . 44 |

| 3.12 | Schematic of asynchronous AER to VTSAER converter. Priority multiplexer reads the privileged (red) channel first, while the AER source                                                                                                                                                          |      |

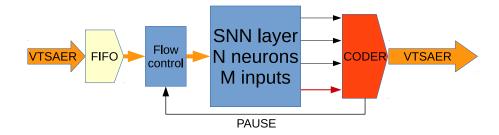

| 3.13 | stream is passing through the 1-element FIFO to avoid data loss Block schematic of the VTSAER data flow through the single-layer SNN. Orange arrows show the VTSAER paths, black arrows correspond to                                                                                           | . 44 |

|      | binary real-time output. Red arrow corresponds to the "timestep neuron" output.                                                                                                                                                                                                                 | . 46 |

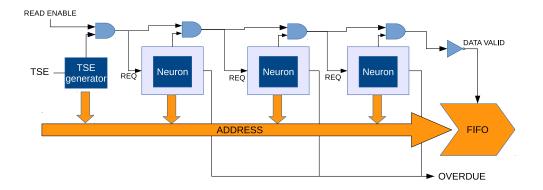

| 3.14 | Hardware architecture of the VTSAER encoder. Spike train, generated                                                                                                                                                                                                                             |      |

|      | by the neuron cores, is converted into the AER stream                                                                                                                                                                                                                                           | 47   |

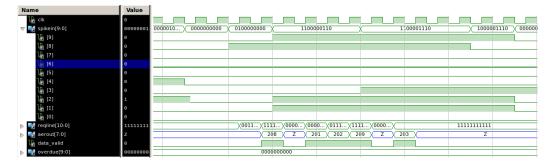

| 3.15 | VTSAER encoder operation. The neurons 8,9,1,2 and 3 generate spikes                                                                                                                                                                                                                             |      |

|      | that are served by the encoder and neuron addresses $(208,201,202,203,209)$ are put on the bus $AEROUT$ . $DATA\_VALID$ signal is connected to the last $REQOUT$ output and is used to push the valid event addresses into                                                                      |      |

|      | the FIFO. Note that the neurons are served in priority order from low                                                                                                                                                                                                                           |      |

|      | numbers to high                                                                                                                                                                                                                                                                                 | 48   |

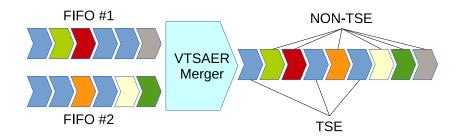

| 3.16 | VTSAER merger operation. TSE events are shown in light blue, non-TSE events shown in other colors. Two streams from FIFOs are merged                                                                                                                                                            |      |

|      | into one stream.                                                                                                                                                                                                                                                                                | 49   |

List of Figures ix

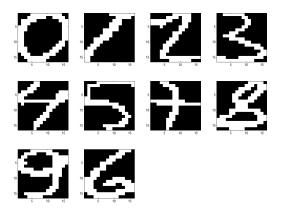

| 4.1  | Patterns for network training of 10 handwritten digits (Semeion dataset).                       | 51 |

|------|-------------------------------------------------------------------------------------------------|----|

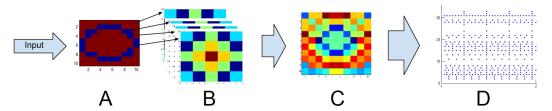

| 4.2  | Image to spike train encoding dataflow. Input image <b>A</b> is processed with                  |    |

|      | RFs of encoding neurons $\mathbf{B}$ , and the result $\mathbf{C}$ is received by encoding neu- |    |

|      | rons, generating the spike trains $\mathbf{D}$ where spike frequency is proportional            |    |

|      | to the intensity of the corresponding pixel and its surroundings                                | 52 |

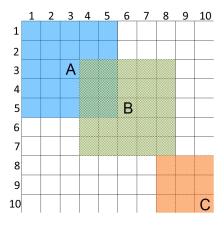

| 4.3  | Three receptive fields in a 10x10 input space. Blue field corresponds to                        |    |

|      | the neuron A (3,3 in input matrix). Green field corresponds to neuron                           |    |

|      | B (6,5) and orange corresponds to neuron C (10,10). Note that only the                          |    |

|      | active part or RF is shown.                                                                     | 52 |

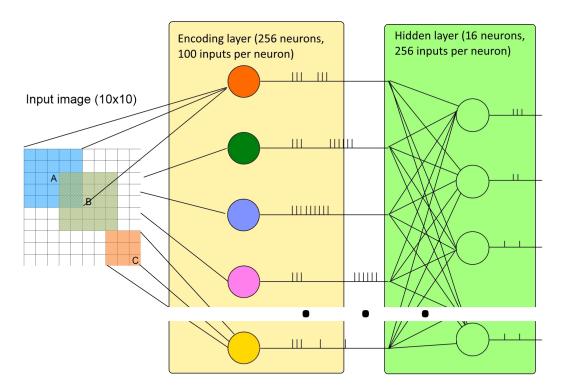

| 4.4  | Network structure used in the simulation. Input space of 10x10 is con-                          |    |

|      | verted into a spike train by a matrix of 10x10 input neurons with the 5x5                       |    |

|      | receptive field. The generated spike train is fed to the hidden layer of                        |    |

|      | 16 simplified LIF neurons with training. Not all connections between the                        |    |

|      | input space and encoding layer are shown                                                        | 54 |

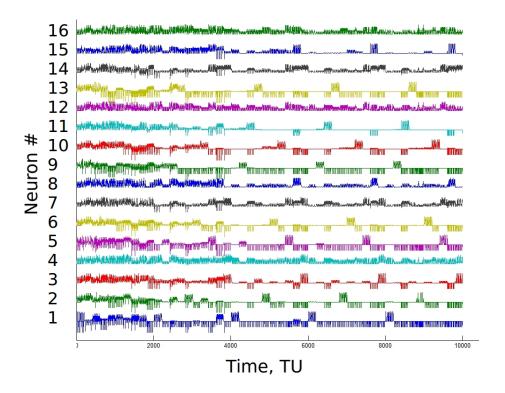

| 4.5  | Membrane potentials of neurons during training. At the beginning, neu-                          |    |

|      | ronal reactions are chaotic. The training leads to sharp individual neu-                        |    |

|      | ronal reactions, and neurons become specific to one pattern. The most                           |    |

|      | intensive weight shaping occurs between 3000 and 4000 TUs                                       | 55 |

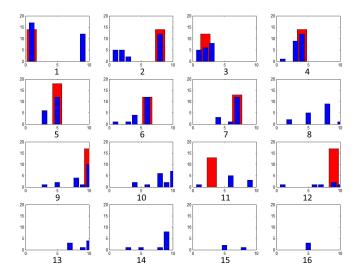

| 4.6  | Spike rate per sample before and after training. Blue bars are spike rate                       |    |

|      | before training and red ones represent the spike rate after the training.                       |    |

|      | Neurons 8,10,13,14,15,16 did not learn any pattern                                              | 55 |

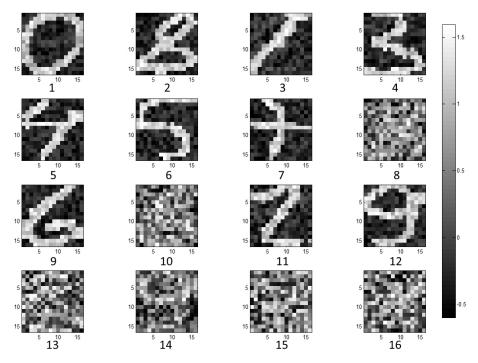

| 4.7  | Neurons weights representation after STDP training. Ten out of sixteen                          |    |

|      | neurons learned to discriminate all ten numbers in the SEMEION dataset.                         | 56 |

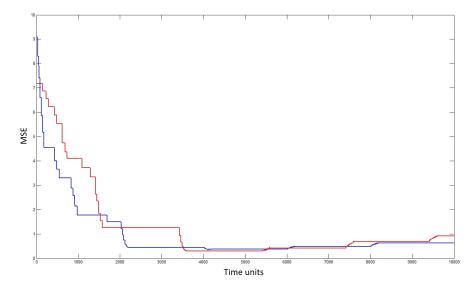

| 4.8  | MSE for single pattern during learning. Red line represents the simplified                      |    |

|      | model, blue represents classic LIF. It can be seen that, after 5000 TU,                         |    |

|      | neuron becomes overtrained for both models and MSE is similar                                   | 56 |

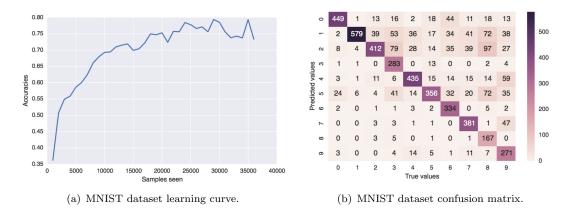

| 4.9  | evtCD RBM with classic LIF neuron learning curve and confusion matrix.                          | 58 |

| 4.10 | Final learned weights for the evtCD RBM with LIF neuron. The weights                            |    |

|      | are similar to weights learned by a classic RBM or autoencoder                                  | 59 |

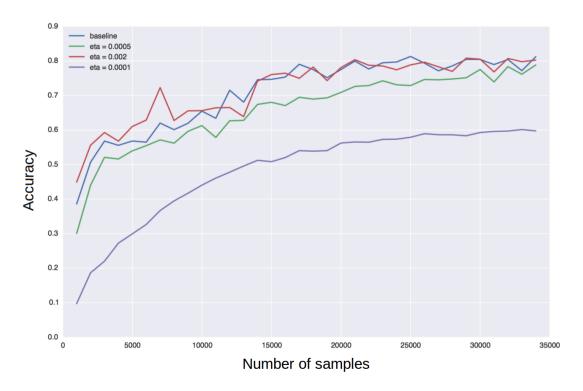

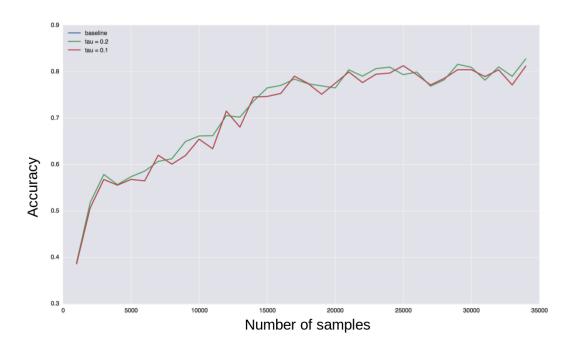

|      | evtCD RBM with LIF neuron learning curve for different learning rates                           | 60 |

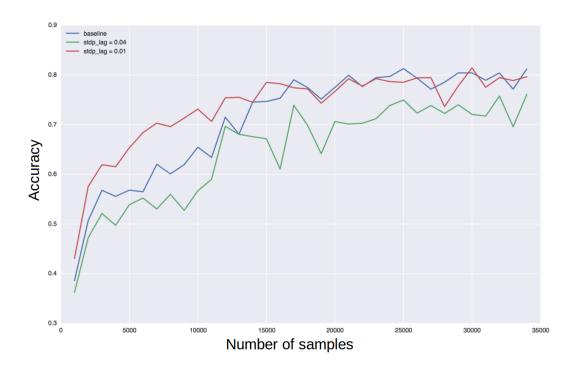

|      | evtCD RBM with LIF neuron learning curve for different STDP length                              | 61 |

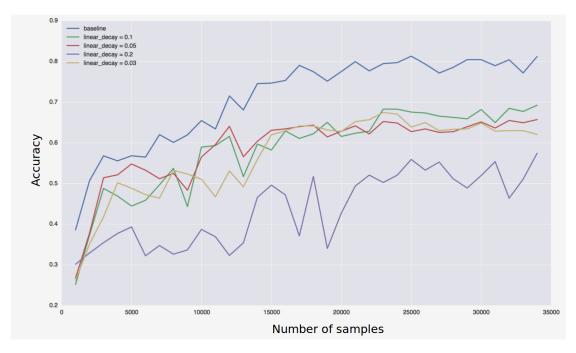

| 4.13 | evtCD RBM with LIF neuron learning curve for different membrane decay                           |    |

|      | constant.                                                                                       | 61 |

| 4.14 | evtCD RBM with simplified LIF neuron learning curve for different mem-                          |    |

|      | brane decay constant                                                                            | 62 |

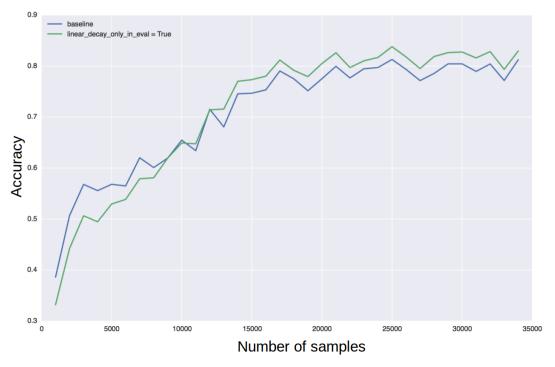

| 4.15 | Learning curve for evtCD RBM trained with classic LIF and evaluated                             |    |

|      | with the simplified model                                                                       | 62 |

| E 1  | DCD40E1 block ashamatic Courses [57]                                                            | ce |

| 5.1  | DSP48E1 block schematic.Source: [57]                                                            | 66 |

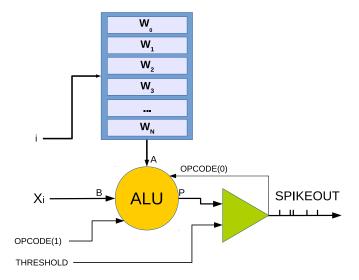

| 5.2  | Simple neuron block schematic                                                                   | 68 |

| 5.3  | Neuron with shift-based decay block schematic. D is a constant value                            |    |

|      | controlling the membrane potential decay $2^{-D}$                                               | 70 |

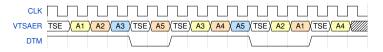

| 5.4  | Interleaved VTSAER stream                                                                       | 71 |

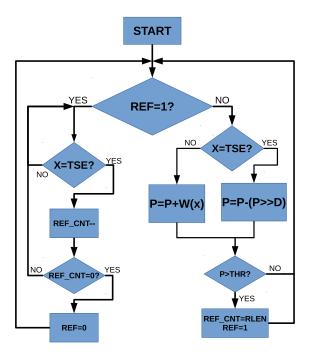

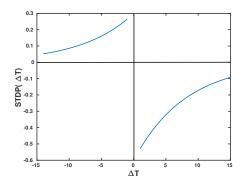

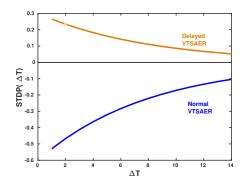

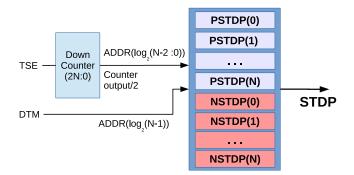

| 5.5  | The conversion of STDP function for IVA , with only positive values of $\Delta t$ .             | 72 |

| 5.6  | Block schematic of STDP. Note that STDP is a function of counter                                |    |

|      | REF CNT and delayed/normal stream flag DTM                                                      | 72 |

List of Figures x

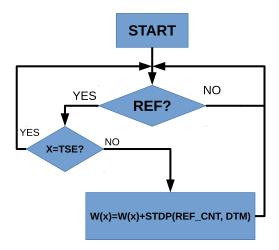

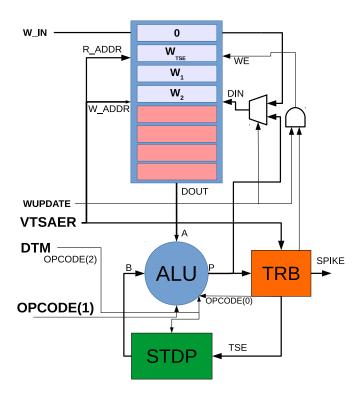

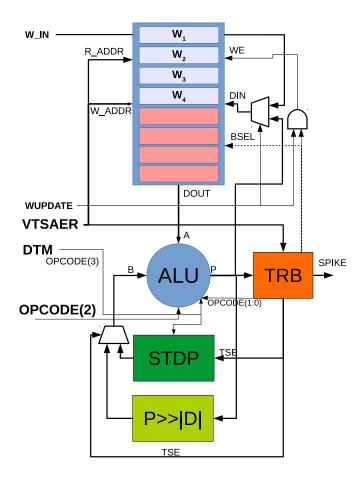

| 5.7  | PFGA implementation of linear decay neuron. The STDP block and DTM (Delayed Timeslot Marker) input are not used in a version without learning. The untitled top block is the weight memory (containing 0 as null event weight and TSE membrane leakage weight). The saturated arithmetic ALU is in the center.                                                                                     | 73 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.8  | FPGA implementation of shift-based nonlinear decay neuron. The TRB is detecting TSEs, switching the multiplexer on ALU port B and changes the ALU opcode from $P = P + A$ to $P = P - B$ operation. Block on the bottom is a binary shifter.                                                                                                                                                       | 75 |

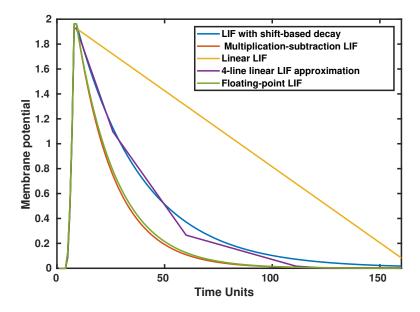

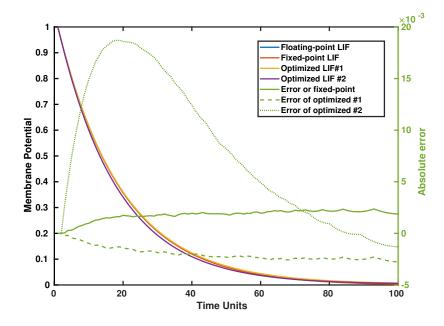

| 5.9  | Comparison of decay curves for various membrane potential decay algorithms. The reference curve is the green one, computed with 64-bit floating point. All other algorithms were using Q6.12 fixed-point arithmetic.                                                                                                                                                                               | 76 |

| 5.10 | Comparison of decay curves and absolute error for subtraction-multiplication based decay algorithms.                                                                                                                                                                                                                                                                                               |    |

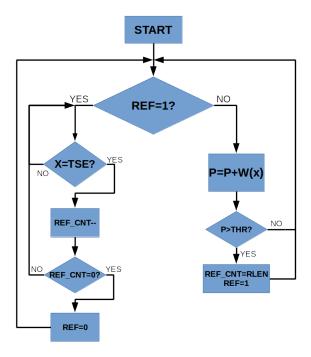

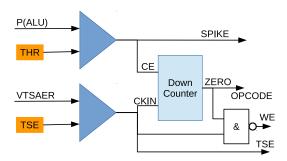

| 5.11 | Threshold and Refractory Block schematic (TRB). It consists of a comparator, pattern detector, a counter and a 2NAND gate to generate a WE                                                                                                                                                                                                                                                         |    |

| 5.12 | signal for the STDP weight update                                                                                                                                                                                                                                                                                                                                                                  | 78 |

|      | configuration, ROM can be treated as two-bank memory, where DSM is the bank select bit                                                                                                                                                                                                                                                                                                             | 79 |

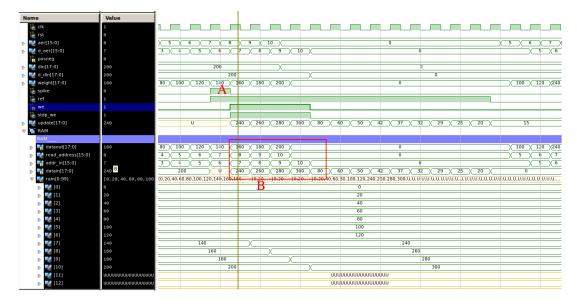

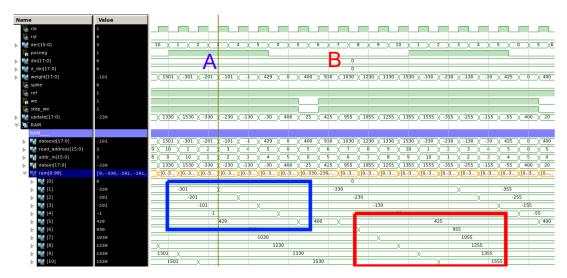

| 5.13 | The simulation of single STDP series. The spike, marked as red A, causes the potentiation of the weights $\#7,8,9,10$ . The addresses and values are highlighted by a red rectangle, marked as B                                                                                                                                                                                                   | 81 |

| 5.14 | Simulation of multiple STDP series. Memory values are at the bottom. In the depression phase, marked with blue A ( <b>posneg</b> signal is high), the weights #1 to 5 are depressed (blue rectangle). In the potentiation phase, marked with red B, the weights #5 to 10 are potentiated (red rectangle). Note that the weight #5 is both depressed and potentiated during one refractory period.  | 82 |

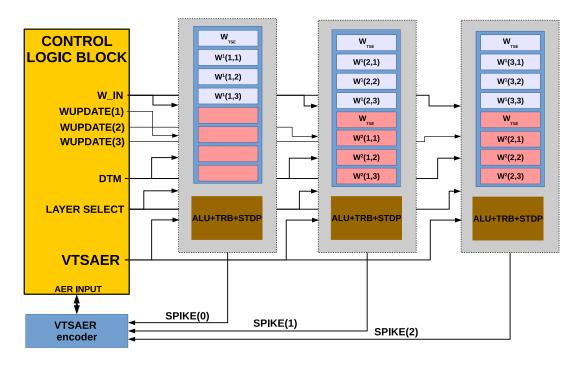

| 5.15 | 3-3-2 network schematic. Hidden layer weights are stored in the upper memory bank, and output layer weights are stored in the lower memory bank. All signals beside SPIKE and WUPDATE are common for all neurons.                                                                                                                                                                                  | 83 |

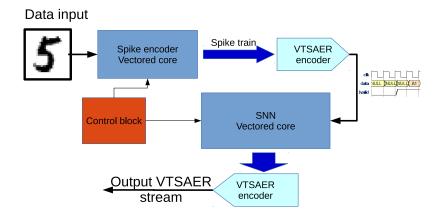

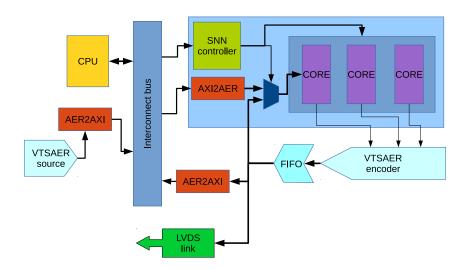

| 5.16 | Neuromorphic real-time processing system layout. The non-spiking input is encoded into spikes with the vectored RF architecture described in 6. The result is encoded into VTSAER using mapper block, and the encoded VTSAER stream is processed by the dedicated SNN core.                                                                                                                        | 86 |

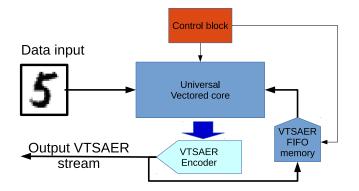

| 5.17 | Neuromorphic processing system layout with one universal core. The similarity in the RF encoding and SNN architectures make the combined vectored core possible. The core is encoding the input sample first and the resulting spike train is encoded into the VTSAER stream and stored in FIFO. After that, the VTSAER is read from the FIFO and processed in the universal core in the SNN mode. | 87 |

| 5.18 | Possible SoC schematic utilizing the proposed core                                                                                                                                                                                                                                                                                                                                                 |    |

List of Figures xi

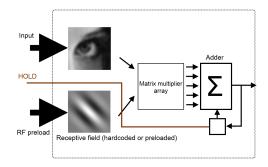

| 6.1 | Implemented system schematic                                                | 90 |

|-----|-----------------------------------------------------------------------------|----|

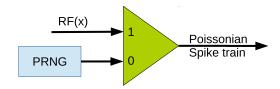

| 6.2 | Poissonian spike generation with the PRNG and comparator                    | 91 |

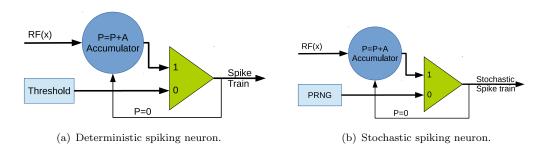

| 6.3 | Integrate-and-Fire neuron for deterministic and stochastic spike train gen- |    |

|     | eration.                                                                    | 92 |

| 6.4 | Frobenius inner product module                                              | 93 |

| 6.5 | Vectored implementation of RF neuron                                        | 95 |

| 6.6 | Hardware simulation of a neuron. Easy to notice how ISI is changing         |    |

|     | from the infinity (no spikes, response is below threshold) to 4 and then    |    |

|     | to 3 clock cycles                                                           | 96 |

# List of Tables

| 3.1 | Truth table for the single neuron VTSAER encoder. STATE is the internal variable of the encoder, SPIKEIN and REQ are inputs, REQOUT                                                                               |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | and OVERDUE are outputs                                                                                                                                                                                           | 47  |

| 3.2 | Hardware occupation of the VTSAER encoder without FIFO. The synthesis was made for Virtex 7 xc7vx485t device                                                                                                      | 48  |

| 4.1 | Simulation speed of classic LIF and simplified LIF model networks. All data are obtained on synthetic datasets taking the mean values of 5 runs.                                                                  | 57  |

| 5.1 | Hardware occupation of single automata neuron                                                                                                                                                                     | 80  |

| 5.2 | Hardware occupation of layers of different size                                                                                                                                                                   | 83  |

| 5.3 | Hardware occupation of layers of different size                                                                                                                                                                   | 84  |

| 5.4 | Hardware components of 1000-neuron layer and a single neuron. Neurons implemented are linear decay simplified LIF. The numbers are from the RTL logical synthesis, not from the actual FPGA placement. FPGA Place |     |

|     | and Route numbers are in tables 5.2 and 5.3                                                                                                                                                                       | 84  |

| 5.5 | LIF neuron parameters of the selected implementations                                                                                                                                                             | 85  |

| 5.6 | General comparison of the described neurons. Sub-mul neuron uses one additional register. Memory usage refers only to the memory necessary to implement the selected PSP function                                 | 88  |

| 6.1 | Implementation Results for the proposed blocks: Integrate&Fire neuron, a neuron layer of 1024 units and three different Frobenius Inner Product (FIP) encoding block implementations                              | 93  |

| 6.2 | Hardware occupation of single RF Integrate-and-fire neuron                                                                                                                                                        | 95  |

| 6.3 | Accuracy and maximal error for different RF size and fractional part width.                                                                                                                                       |     |

| 7.1 | Comparison of the selected fine-grained spiking neuron hardware implementations                                                                                                                                   | 100 |

#### **Abbreviations**

**AER** Address-Event Representation

ANN Artificial Neural Network

CD Contrastive Divergence

CLB Common Logic Block

DSP Digital Signal Processor

FPGA Field Programmable Gate Array

GRF Gaussian Receptive Field

IVA Interleaved VTSAER

LFSR Linear Feedback Shift Register

LIF Leaky Integrate and Fire

MLP Multi-Layer Perceptron

MSE Mean Squared Error

PSP PostSynaptic Potential

RBM Restricted Boltzmann Machine

ReLU Rectified Linear Unit

RF Receptive Field

SNN Spiking Neural Network

SRM Spike Response Model

STDP Spike Time Dependent Plasticity

TSE TimeStep Event

TU Time Unit

VTSAER Variable TimeSlot length AER

#### Resumen de la tesis doctoral

"Spiking Neural Networks models targeted for implementation on Reconfigurable Hardware – Modelos de redes neuronales de espigas para implementación en hardware reconfigurable"

#### Autor: Taras Iakymchuk

La tesis presentada se centra en la denominada tercera generación de redes neuronales artificiales, las Redes Neuronales Spiking (SNN) también llamadas 'de espigas' o 'de eventos'. Este campo de investigación se convirtió en un tema popular e importante en la última década debido al progreso de la neurociencia computacional. Las Redes Neuronales Spiking, que tienen no sólo la plasticidad espacial sino también temporal, ofrecen una alternativa prometedora a las redes neuronales artificiales clásicas (ANN) y están más cerca de la operación real de las neuronas biológicas ya que la información se codifica y transmite usando múltiples espigas o eventos en forma de trenes de pulsos. Este campo ha ido creciendo en los últimos años y ampliado el área de ingeniería neuromórfica cuya principal área de trabajo es el uso de VLSI analógicos, digitales, mixtos analógico/digital y software que implementa modelos de sistemas neuronales spiking. Esta tesis analiza las Redes Neuronales Spiking desde la perspectiva de Aprendizaje Automático, donde la plausibilidad biológica no es el objetivo principal, pero la capacidad de crear algoritmos de inteligencia artificial basados en SNN es uno de los objetivos principales, junto con su viabilidad de implementación de hardware. Con el fin de cumplir con los objetivos, varios modelos neuronales y topologías de red son revisados y comparados. La codificación de picos o la representación de datos con los picos también se discute en este trabajo.

El desarrollo de topologías SNN y algoritmos capaces de proporcionar capacidades de inteligencia artificial basadas en espigas de entrada al sistema es uno de los principales temas de esta tesis. Sin embargo, se hace también hincapié en su implementación hardware ya que existen modelos complejos para SNN que en muchos casos no son viables para sistemas en tiempo real y requieren de sistemas de alta capacidad computacional para ser ejecutados.

El tema principal de la investigación en este trabajo es la evaluación de algoritmos

existentes y el desarrollo de nuevos algoritmos, estructuras de datos y métodos de codificación para la implementación hardware de las redes neuronales de spiking, especialmente dirigidas a FPGA (Field-Programmable Gate Arrays). Los dispositivos FPGA son elegidos debido a sus excelentes capacidades de cálculo paralelo masivo, bajo consumo de energía, baja latencia y versatilidad. En los últimos años, las FPGA se convirtieron en una popular plataforma para tareas clásicas de aprendizaje de máquinas, tales como reconocimiento de imágenes, control automático, predicción de series temporales, robótica, etc. Así, la tesis investiga todas las cuestiones relacionadas con el despliegue de un sistema completo de hardware basado en espigas, desde la codificación de información externa como entradas hasta la salida final de un sistema de inteligencia artificial basado en SNN, incluida la optimización en la transmisión de datos, y todo ello implementado en arquitecturas hardware que optimizan el rendimiento y permiten la implementación de redes spiking de un elevado número de neuronas.

Se propone una nueva arquitectura simplificada de neuronas de tipo LIF (Leaky Integrateand-Fire). La neurona se evalúa para redes de tipo Perceptron y Restricted Boltzmann

Machine (RBM) para probar su rendimiento. Además, las capacidades de aprendizaje

de las redes propuestas se desarrollan mediante la definición de un procedimiento optimizado para el aprendizaje de STDP (Spike Time Dependent Plasticity). Las propuestas

de optimización en software son completadas por nuevas arquitecturas de hardware, especialmente diseñadas para la implementación de FPGA.

En lo que se refiere a las arquitecturas de hardware, esta tesis define la llamada "neurona autómata", basada en un formato de representación de espigas novedoso también y definido en esta tesis, llamado 'Variable Timeslot Length Address-Event Representation' (VTSAER). Este formato tiene una mayor versatilidad que anteriores propuestas de AER, eliminando la necesidad de marcas de tiempo y permitiendo un verdadero sincronismo de cualquier número arbitrario de eventos. La estructura del VTSAER permite procesar la información en las neuronas de espigas como un autómata finito alimentado por eventos. Este nuevo enfoque ayuda a separar el estado del sistema de la tasa de entrada de datos y reducir el número de canales de entrada/salida.

Otra novedad propuesta en esta tesis es una arquitectura vectorizada de capas de las redes neuronales. Esta arquitectura permite calcular el estado de cualquier número arbitrario de capas reutilizando los mismos bloques neuronales de hardware varias veces. Este concepto de procesamiento vectorial de datos se puede aplicar no sólo en las redes neuronales de espigas, sino también en redes neuronales clásicas no-spiking de tipo

ANN y otros algoritmos de aprendizaje automático. Con la arquitectura vectorizada y la neurona autómata, el factor limitante para el tamaño de la red es sólo la cantidad de memoria en el FPGA, lo que es una mejora significativa a las implementaciones anteriores. En cuanto a los algoritmos de aprendizaje para SNN, esta tesis describe una nueva aplicación del algoritmo de aprendizaje más popular para las redes neuronales spiking, derivado de las observaciones de los fenómenos biológicos. Implementaciones de hardware digital de la STDP rara vez se encuentran dado que el algoritmo está utilizando causalidad de sincronización hacia atrás que requiere un empleo significativo de recursos de hardware. La nueva implementación propuesta en esta tesis está resolviendo el problema de causalidad con una sobrecarga de hardware muy pequeña. La versión mejorada de STDP se puede utilizar en redes de número arbitrario de neuronas. El proceso de actualización de pesos es independiente para cada neurona y no afecta al flujo global de entrada de espigas.

La implementación FPGA de algoritmos de codificación visual también se cubre en esta tesis. Se describe la codificación de campos receptivos visuales tipo Gabor y se presentan dos implementaciones de hardware. El método de codificación de campo receptivo es muy similar a la operación de convolución utilizada en redes neuronales no-spiking. Los campos específicos de orientación de Gabor son importantes en el procesamiento de imágenes, ya que son fenómenos bien estudiados observados en la corteza visual de mamíferos y se desempeñan bien en el procesamiento de imágenes y en las tareas de codificación de espigas. Las dos propuestas de implementación en FPGA son arquitectura paralela y vectorizada. La comparación se realiza utilizando tamaños de campo receptivo típicamente usados en tareas prácticas que muestran las posibilidades de aplicación para cada una de las propuestas de implementación.

Además, la implementación del hardware digital de algoritmos requiere la adaptación de la aritmética, ya que la aritmética de punto fijo se utiliza para evitar la complejidad adicional dada por los cálculos de coma flotante. Por lo tanto, se realiza un extenso estudio de la aritmética de punto fijo en el hardware de codificación y procesamiento de spikes para probar que el punto fijo es capaz de proporcionar la exactitud y precisión requeridas a un menor costo computacional y de recursos. Todos los algoritmos y arquitecturas propuestos se prueban resolviendo problemas clásicos con bases de datos abiertos (open source) para poder hacer una comparación con otros autores: los conjuntos de datos SEMEION e Iris se utilizan en este caso. Con respecto a los resultados

de hardware, las arquitecturas digitales propuestas permiten una alta frecuencia de operación de reloj, cercana al máximo permitido por el dispositivo FPGA (alcanza hasta 387MHz). Los algoritmos y arquitecturas propuestos también permiten SNN de tamaño arbitrario, limitándose sólo a la capacidad del dispositivo.

Todas las cuestiones antes mencionadas forman una compleja solución novedosa para la implementación de redes neuronales de espigas en hardware FPGA con velocidad de procesamiento varios cientos de veces más rápido que las simulaciones de software y una precisión comparable. Los bloques de hardware propuestos son versátiles, capaces de implementar una amplia gama de modificaciones de los algoritmos descritos y adaptar múltiples topologías SNN con diferentes números de entradas, número de capas, número de neuronas por capa, número de salidas, longitud de bits y, en general, aquellos parámetros que permiten implementar múltiples formas de SNN.

En total, utilizando los bloques de hardware desarrollados en esta tesis, es posible construir un sistema neuromórfico masivo autosuficiente con un ciclo de procesamiento completo hecho dentro de un chip. De este modo, los sistemas neuromórficos podrían ser implementados a un costo menor en términos de desarrollo y tiempo de diseño, junto con placas de hardware más simples.

Esta tesis doctoral, además del primer capítulo introductorio, está estructurada en varios capítulos.

#### 0.1 Capítulo 2

Se realiza una descripción general de las redes neuronales comenzando por las clásicas redes neuronales artificiales para continuar por los modelos de redes neuronales pulsantes o 'spiking', sus topologías y las metodologías de aprendizaje, haciendo especial énfasis en las técnicas de aprendizaje basadas en la plasticidad. Se describen los modelos biológicos así como los modelo simplificados de Hodgkin-Huxley, Izikevich, LIF (Leaky-Integrate and Fire) y su generalización denominada Spike Response Model (SRM) que define un potencial interno de la neurona (Post Synaptic Potential – PSP) basado en los estímulos recibidos en el transcurso de un tiempo y, si el potencial supera un determinado umbral, la neurona genera un estímulo de salida.

Tras la descripción de los modelos generalmente empleados, esta tesis propone un modelo simplificado de neurona que facilita el cálculo del potencial con vistas a su implementación hardware, reduciendo el uso de recursos lógicos y optimizando la velocidad de operación del sistema. Finalmente, se describen las redes neuronales pulsantes de tipo Multiplayer Perceptron y Restricted Boltzmann Machine (RBM) incluyendo los modelos de aprendizaje STDP y evtCD, que serán utilizadas en capítulos posteriores.

#### 0.2 Capítulo 3

Los sistemas de codificación de la información en estímulos (también llamados pulsos, o eventos) resultan de gran importancia para el posterior análisis de los mismos y un correcto diseño de las redes neuronales que los analizan. Se describen los modelos de codificación en frecuencia, Gaussian Receptive Fileds (GRF) y campos de recepción visuales. Por otra parte, dado el alto número de datos que se generan, se describen modelos de transmisión de la información como Address Event Representation (AER). En este sentido se propone una variante que se ha denominado 'Variable Time Slot Length AER' (VTSAER) que optimiza y mejora la recepción de los eventos por parte de las neuronas, especialmente a la hora de tratar los eventos recibidos para el cálculo del potencial interno. Como parte final del capítulo, se describe el proceso desarrollado para poder codificar los estímulos en el formato VTSAER propuesto.

#### 0.3 Capítulo 4

Esta parte de la tesis evalúa el comportamiento de los nuevos modelos propuestos mediante la aplicación de diferentes conjuntos de datos de entrada y su comparación con otros modelos. Para ello, se toma el conjunto de imágenes de dígitos manuscritos, se le aplica la codificación de campos receptivos de 5x5 en una capa de 256 neuronas de codificación y posteriormente se utiliza una capa de 16 neuronas LIF. Posteriormente, se realiza un entrenamiento STDP con estrategia 'winner depresses all' en lugar de la comúnmente empleada de 'winner takes all'. Tras el entrenamiento, se observa que 10 de las 16 neuronas de la capa LIF son capaces de generar una frecuencia de salida de pulsos

específicamente asociada a cada uno de los dígitos (0 al 9). En comparación con otros modelos con el mismo resultado, el tiempo de ejecución es mucho menor para el modelo propuesto (del orden de 15 a 20 veces menor, en función del número de neuronas). Como segunda comprobación, se plantea una red de tipo Boltzmann (Restricted Boltzmann Machine, RBM) con aprendizaje de tipo evtCD para resolver la clasificación del conjunto de datos MNIST consistente en imágenes de tamaño 28x28 píxeles. Por tanto, se tiene una capa de entrada de codificación de eventos de 784 neuronas. Se plantea una segunda capa de 100 neuronas LIF. En comparación con otros modelos LIF, el modelo simplificado propuesto en este trabajo presenta un porcentaje más bajo que el modelo no simplificado (71% y 80%, respectivamente). En cambio, se observa que los resultados en fase de validación son similares en ambos modelos, lo que plantea la opción de realizar el entrenamiento con un modelo no simplificado para posteriormente aplicar los pesos obtenidos a las neuronas simplificadas; esta posibilidad es factible en numerosas aplicaciones donde se realiza un entrenamiento 'off-chip' para posteriormente realizar la ejecución del modelo en aplicaciones de tiempo real 'on chip' con el modelo simplificado.

#### 0.4 Capítulo 5

Dado que los nuevos modelos propuestos están orientados a su utilización en sistemas hardware de tiempo real, este capítulo detalla las arquitecturas hardware planteadas para su implementación eficiente. Los actuales dispositivos FPGA contienen, además de recursos configurables, unidades de cálculo tipo ALU (denominadas bloques DSP) y bloques de memoria RAM distribuida internamente (BRAM). Por ello, la implementación de los modelos neuronales propuestos tienen en cuenta el uso intensivo de estos recursos para optimizar la arquitectura hardware completa, reduciendo el uso de recursos lógicos a emplear y aumentando la velocidad de operación del hardware. En primer lugar, se asume que la entrada de las neuronas estará codificada según el algoritmo VTSAER, de modo que para todas las neuronas de una misma capa, la misma entrada es aplicada a todas ellas en un instante determinado, procesándose las entradas de modo serie (una tras otra). Por otra parte, cada neurona se puede considerar un autómata de estados finitos donde el estado de la neurona depende del estado en el instante anterior y de la entrada, existiendo una evolución de los estados para generar un estímulo de salida

en caso de que el potencial interno de la neurona supere el umbral definido. Para la arquitectura interna de la neurona, se proponen dos modelos: 'binary shift-based LIF' y 'multiplication-based LIF'. La diferencia entre estos modelos radica en el modo de cálculo del potencial de neurona dado que, en un caso, el cambio de potencial ante la recepción de estímulos se realiza en base al desplazamiento de un valor potencia de dos (equivalente a una multiplicación) y en el otro caso, se utiliza directamente la multiplicación, siendo más preciso el cálculo del potencial, pero requiriendo del multiplicador. Este capítulo describe también la implementación del algoritmo de aprendizaje STDP para las neuronas de estímulos, raramente implementado en hardware debido a la complejidad en el cálculo de tiempos entre la aparición de estímulos de entrada y salida, haciendo necesario el empleo de un hardware complejo. Esta tesis propone en cambio un sistema de entrenamiento STDP con el empleo de un bajo número de recursos y asumiendo, como en el caso de las neuronas LIF simplificadas, el uso de entradas neuronales codificadas mediante VTSAER con una señal de marcación (interleaved VTSAER) para indicar la llegada de entradas retardadas, o bien actuales, permitiendo la obtención de tiempos entre estímulos de modo más directo y realizando el entrenamiento mediante un procedimiento realmente sencillo. La implementación hardware de una neurona de este tipo se realiza de modo que es posible optar por su implementación incluyendo aprendizaje o bien sólo cálculo de entradas, pesos, potencial y generación de salida. Recordemos que numerosas aplicaciones no requieren de entrenamiento 'on-chip', con lo que resulta conveniente que la neurona lo permita, pero se pueda configurar antes de implementar el sistema, con el consiguiente ahorro de recursos lógicos. La neurona está basada en el empleo de un bloque interno de memoria BRAM para almacenamiento de pesos de cada entrada de la neurona, una ALU que contiene un bloque DSP para cómputo aritmético del potencial. Se plantean cuatro variantes: función de potencial lineal, función de potencial con desplazamiento, función de potencial con multiplicación, y función de potencial con multiplicación optimizada en base a la combinación restamultiplicación. Además, se realiza un análisis del tipo de curva de potencial obtenido para cada una de las versiones.

Para concluir el capítulo, se describe la arquitectura completa de una red neuronal con varias capas, mostrando implementaciones de hasta mil neuronas por capa, siendo importante remarcar que el uso de varias capas supone únicamente un incremento en la memoria empleada para el almacenamiento de los pesos ya que el resto del hardware se reutiliza. Se realiza además un análisis de las limitaciones del uso de sistemas de punto

8 ABBREVIATIONS

fijo como es el caso y de los errores producidos en base al tamaño de bits empleado. Con todos los bloques de implementación descritos en este capítulo, resulta posible el desarrollo completo de un sistema neuromórfico capaz de procesar las entradas y generar a un flujo de datos de salida de tipo VTSAER tras su procesado por parte de una red neuronal.

#### 0.5 Capítulo 6

Para los casos en los que las entradas al sistema no sean de tipo 'spike', este capítulo ofrece el sistema hardware que permite la codificación en pulsos según los algoritmos descritos en el capítulo 3, mediante neuronas de codificación. Se proponen cuatro posibles arquitecturas de neuronas de codificación: neurona IF ('integrate and fire'), y neurona con campo receptivo 8x8 Frobenius Inner Product (FIP) implementada de tres formas diferentes (con módulo DSP, con bloques lógicos CLB y con bloques CLB sin posibilidad de reparametrización. Para el cómputo completo de una capa de neuronas de codificación, se describen dos tipos de arquitecturas hardware, una de tipo vectorial y otra de tipo paralelo comparando los resultados a nivel de eficiencia y de precisión de cálculo en función del número de bits empleados.

#### 0.6 Capítulo 7

Este capítulo presenta las conclusiones del trabajo y realiza una comparativa con los resultados obtenidos por otros autores, mostrando los tipos de trabajos presentados hasta el momento en este campo y las posibilidades que la implementación de sistemas neuromórficos ofrece en el futuro, mediante el uso de plataformas hardware adaptables a múltiples tipos de redes neuronales, topologías de interconexión, configuración y entrenamiento para los pesos de las conexiones, etc. En general, se abre el camino para la implementación de sistemas neuromórficos con un alto número de neuronas en dispositivos FPGA de bajo consumo y alta velocidad de operación.

#### Chapter 1

#### Introduction

#### 1.1 Goals and aims of this thesis

In this thesis, I studied the feasibility of implementing Spiking Neural Networks (SNNs) in reconfigurable hardware. The main research is focused on efficient computation models for the SNNs and the hardware architecture that will boost the performance of those models. The stress was put on the practical applications of the SNNs, rather than on a biological plausibility. The targeted platform are the widespread Field-Programmable Gate Array (FPGA) devices.

In the recent years, the field of Spiking Neural Networks and Neuromorphic Hardware is the area of special interest. The advantages of this approach: low power, low latency combined with the outstanding cognitive capabilities of the spiking networks are attracting more and more researchers. Neuromorphic hardware finds the way to the commercial market, with the companies like IBM developing TrueNorth spike-operating neuroprocessor and Qualcomm with Zeroth neuroprocessor. However, a number of topics in the hardware implementation of a spike-based system still needs to be researched. The dramatic difference between spiking computation paradigm and the classic ones requires novel approach for maximum utilization of its benefits.

To develop the proposed architectures, an extensive study of existing neuronal and networks models was performed. As the data representation plays important role in the properties and performance of the network models, various types of data conversion and representation were studied. Extra effort was dedicated to Address-Event Representation (AER) protocol, as this data representation is widely used in the existing spiking

hardware. In addition, several learning algorithms for SNNs were evaluated from the perspective of their implementation in hardware, since the existing computing models and algorithms are not suited for direct implementation in reconfigurable hardware. The conducted research deals with the hardware implementation problem globally: neural coding, neural models, network topology, computer arithmetic and network connectivity protocols. A novel neuron model is proposed, optimized for the fixed-point arithmetic. The new type of vector architecture, based on the given neuron model, is created and tested to prove its feasibility. A novel version of Address-Event Representation protocol is proposed to be used for this implementation, this new version has several advantages over the existing realizations. The proposed hardware and software components can be used to build massive parallel SNNs on a single chip. Networks with several thousands of neurons are possible to implement within one modern FPGA. The developed system is a full neuromophic processing system: from raw data encoding to the classified values output.

#### 1.2 Structure of this thesis

The current thesis is structured as follows:

- Chapter 2 gives a brief overview of the neural networks field, starting from classic ANNs. Spiking neural models, plasticity and neural network topologies are discussed. This chapter introduces the novel linear simplified spiking model, proposed in this thesis.

- Chapter 3 describes the spike encoding, data representation types for spiking neural networks. A large part of this chapter describes the encoding of graphical information since image recognition tasks are one of the most used applications for neural networks. The Address-Event Representation (AER) format is discussed and a novel variation, called Variable Time Slot length AER (VTSAER) is described.

- Chapter 4 contains the evaluation of the simplified neural model in software. Two types of spiking networks, a feedforward perceptron with Gabor-like Receptive Fields encoding and a Restricted Boltzmann Machine are trained and evaluated.

- Chapter 5 describes the hardware implementation of the proposed neural model and data representation. This chapter describes several novel models of spiking neurons, a vectored large-scale neural architecture and a new implementation of the STDP learning algorithm in hardware. The developed components are analyzed from the perspective of speed, occupation, and accuracy in comparison to softwareimplemented models. The benefits and the limitations of the contemporary FPGA devices and fixed-point arithmetic are discussed.

- Chapter 6 is dealing with the hardware implementation of Gaussian Receptive Field (GRF) encoding, described in Chapter 3. Two approaches, parallel and vectored, are implemented, tested and compared.

- Chapter 7 contains the summary of the thesis and comparison with the state-ofthe-art implementations.

#### Chapter 2

# Neural networks and models: a brief overview

In the middle of  $20^{th}$  century, a combination of biological studies with the mathematical approach to the theory of control created a new scientific discipline: artificial neural networks. An artificial neural network is generally defined as a mathematical model, loosely based on the behavior of the animal neural systems. Such models usually consist of computation units (neurons), connected by data paths (synapses) and are able to solve the vast variety of recognition, control, and system identification problems. The pioneering work in this discipline was made by Warren McCulloch and Walter Pitts [1]. They succeeded in creating a mathematical description of an integrating neural element and the model of connections in the networks of such elements. In their work, they demonstrated that a network of simple non-linear integrators can successfully approximate a number of functions. However, the algorithm to design such networks remained unclear until 1949, when Donald Hebb discovered the learning rule, named after him.

"When an axon of cell A is near enough to excite cell B and repeatedly or persistently takes part in firing it, some growth process or metabolic changes take place in one or both cells such that A's efficiency as one of the cells firing B, is increased" Hebb, D.O. (1949), "The organization of behavior", New York: Wiley, p.62 [2]

"When one cell repeatedly assists in firing another, the axon of the first cell develops synaptic knobs (or enlarges them if they already exist) in contact with the soma of the second cell." Hebb, D.O. (1949), "The organization of behavior", New York: Wiley, p.63

"The general idea is an old one, that any two cells or systems of cells that are repeatedly active at the same time will tend to become 'associated', so that activity in one facilitates activity in the other." Hebb, D.O. (1949), "The organization of behavior", New York: Wiley, p.70

The first self-learning artificial neural network was the Mark 1 Perceptron machine, created in 1958 by Frank Rosenblatt [3]. It featured two layers (input and output, no hidden layer) of McCulloch-Pitts neurons with binary function and was able to learn the linearly separable classes. The early success of relatively simple hardware and mathematical models draw interest into the neural networks field, but it quickly went down in 1969 after a publication of Minsky and Papert, who described the limitations of the perceptron model and its learning rule. The influence of this book was so strong, that very little research was done for the next 20 years, and several important works in this field were unnoticed, including the backpropagation algorithm. Note the complexity of wiring of the Perceptron hardware, shown in Figure 2.1. The connectivity problem (number of connections grows exponentially with the number of neurons) remains an important problem even now, 60 years later. The architecture described in this thesis is created to avoid this problem by taking the vectored approach to the computations necessary.

The backpropagation algorithm was rediscovered in 1986, and the application of this method for the neural network training by Rumelhart, Hinton, and Williams ([4]) allowed to successfully train multilayer perceptrons, capable of solving complex nonlinear problems. From the 90s, the neural networks field became active again, what lead to the development of a broad diversity of topologies, learning algorithms, coding methods, and applications.

#### 2.1 Biological neurons and neural models

Wolfgang Maass [5] proposed the three-generation classification scheme for the neural networks. The first generation of neural networks works only with binary [0,1] signals and uses a step function to provide a binarized [0,1] output. The perceptrons belong to the first generation. A perceptron computation unit consists of an adder and a threshold

Figure 2.1: Mark I perceptron, the first neural network device. Note the amount and complexity of wiring. The connectionist problem (number of connections per node) remains an important issue even now, in 2017.

FIGURE 2.2: First generation McCulloch-Pitts perceptron schematic.

comparator, as shown in Figure 2.2. If the sum of weighed binary values is greater than the selected threshold, the output switches to 1.

The second generation works with continuous analog values, usually scaled to the small numeric range and uses a non-linear activation function evaluator. The computing unit, or neuron, is similar to the McCulloch-Pitts neuron. It consists of a multiply-accumulate unit computing the weighted sum of the inputs and the non-linear, usually sigmoid activation function. The output of the sigmoid function is usually bound between [0..1] for the logistic function or [-1..1] for the hyperbolic tangent. In recent years, a novel

Figure 2.3: Sigmoid function neuron schematic. Image courtesy: Tom M. Mitchell. Machine Learning.McGraw Hill. 1997. [7]

Figure 2.4: Spiking neuron model. The output sequence of spikes is computed as a function of input X and time t.

simplified Rectified Linear Unit (ReLU) activation function became popular [6]. The ReLU neurons are computationally simpler and provide a resulting accuracy comparable or even better than traditional sigmoid ones. The schematic of the generic second generation neuron is shown in Figure 2.3.

This work is focused on the third generation of the neural networks, the spiking neural networks [5]. The concept of a spiking neuron is more complex compared to second generation artificial neuron, as the output of the neuron is not only the function of its input (spatial dependency) but also the time. The spiking neuron, shown in Figure 2.4 can change its state even in absence of input stimuli. As the spiking network has both spatial and temporal dependency, its computing capabilities now can include complex processes and transitions. In the spiking neural network, the data are encoded in the series of short pulses, or spikes, transmitted along the data lines, called synapses. The neuron can generate a spike under certain conditions, and these conditions are described by its mathematical model.

The neuron model has a number of tunable parameters, which are important to its functioning. We can change the synaptic weights, transmission delays, stimulation threshold and post-spike response, as well as a number of other parameters. The proper choice of all mentioned variables is crucial for the proper network functionality. The neural models used in this work are described in section 2.3.

#### 2.2 Neural plasticity

There would be a little use of neural networks if they would not have the ability to learn new things by tuning their parameters. The process of adaptation of the network parameters in such form that improves the network response to a given stimuli is called learning. The neural network learning is quite different from the colloquial meaning of this word. S.Haykin [8] defines it as: Learning is a process by which the free parameters of a neural network are adapted through a process of stimulation by the environment in which the network is embedded. The type of learning is determined by the manner in which the parameter changes take place. Generally speaking, neural network learning algorithm can be described by the following cycle:

- 1. The network is given the input, containing the sample of the signal.

- 2. The network generates an output.

- 3. The network output is evaluated using some kind to metrics to determine the current fitness of the network.

- 4. The parameters of the network are tuned with regard of the metrics output from the previous step.

- 5. The steps 1-4 are repeated until the desired fitness is reached.

There are several types, or paradigms, of learning methods: supervised, unsupervised and reinforced. The most well-known method is the **supervised** learning. During the supervised learning, the network gets input stimuli paired with the desired output response. Knowing the output necessary to be produced, the network can adapt its parameters to fulfill it. Usually, the process of the adaptation is done iteratively, in a number of small steps. The classic example of this type of learning is the previously mentioned backpropagation algorithm applied for the multilayer perceptrons, or Hebbian learning. There are several works regarding the implementation of supervised learning in spiking neural networks (Ponulak and Kasinski, 2011 [9]).

The **unsupervised** learning is done by giving the network only the input stimuli and defining some kind of metrics to estimate the network performance. Such metrics can be the fidelity of the sample reconstruction from the current network state, commonly used for Autoencoder networks, or Restricted Boltzmann Machines. The most common spiking learning rule, the Spike-Time Dependent Plasticity (STDP) is an unsupervised learning algorithm as well [10, 11]. STDP will be further discussed in details.

The **reinforcement** learning requires providing a discrete signal, to inform the network about its performance. The proper outcome of the network is positively reinforced, or rewarded, and the erroneous is punished. The difference between reinforcement and supervised learning is that the network doesn't know the expected outcome, it changes its parameters only in a "reward-punishment" scale. As the neural network has multiple parameters, the learning can be represented as a high-dimensional optimization task. Usually, the learning algorithms are tuning the neuronal weights; however, some of them modify the neuronal thresholds (Diehl et al. [12]). The changes of the neural topology are usually done by eliminating the neurons with the weakest response. This technique is called pruning and is optimizing the network performance as well as its computational complexity.

#### 2.3 Neural models

Due to a very high complexity of living neural cell, spiking neural nets are rarely implemented with high-precision biological models. The most important parts such as potential dynamics, signal propagation, and weight plasticity can be successfully modeled by more simple mathematical descriptions. Multiple spiking neural models exist, but only selected ones are presented in this chapter. The descriptions included here are mostly based on the book *Spiking neuron models: Single neurons, populations and plasticity* by Gerstner and Kistler [13].

The selection of the proper model is a compromise between the degree of biological plausibility and the available computation resources. Classic biological models are focused on the plausibility of the described phenomena and the feasibility of the model to predict the behavior of the model components. Computational neuroscientists are more interested in the model plasticity and large-scale simulation capabilities. In the neuromorphic engineering field, the choice is also limited by the intended hardware platforms

Figure 2.5: Plausibility-complexity comparison. FLOPS scale is for digital implementations [14].