## Lab 1: Introduction to MipsIt

(Updated at 21/01/2019)

Work at home (planned) time: 1:30 h

Lab time: 2:30 h

### 1. Introduction

In this first laboratory session we will study the simulation and assembly programs for the MIPS microprocessor (MipSit), which comprises programming software and a CPU simulator. The simulator enables programs written in assembler or C language to be compiled and simulated. The simulation environment has a memory hierarchy that can be fully configured by the user as well as an input/output system with interrupts and a visualization console. This platform will be used for the first five sessions of Computer Structure Laboratory.

We first describe the components of the programming environment and the procedures to be followed. We then use several examples to show the compilation and simulation methodologies. This strategy will enable us to review and consolidate several concepts seen on previous courses and to review the relationship between the programming language and the computer hardware we are going to study on this course.

These laboratory sessions will reinforce the knowledge students have acquired in their theoretical classes. Students will also continue to develop basic techniques for collecting data and representing those data in table or graph format. Before each laboratory session, all members of each working group are required to read the documentation on the theoretical foundation for the work they will perform and the tools they will use. Preliminary reading of these documents will help them to use the software and laboratory equipment and answer questions on their use and functionality.

In each laboratory session students should create a teamwork methodology that enables them to take maximum profit from the session. You need to be on time and pay attention to the lecturer's instructions. This is important especially for this first session where we will present the ground rules to ensure that all sessions are conducted properly.

#### Goals

On completion of this session you will be able to

- understand the basic components and capabilities of MipsIt,

- configure the MipsIt simulator,

- create a project with MipsIt (Assembler and C (minimal)/Assembler),

- compile/link and simulate a program with MipsIt, and

- understand the interaction between high-level programs and microprocessor components, i.e. data storage, variable alignment, and the read/write operations of I/O devices.

#### Resources

For these laboratory classes a personal computer will be available with the Windows operating system and the MipsIt simulator. The MIPS simulator can be downloaded for Windows from the *Aula Virtual*. The file must be unzipped and stored in any directory under any name without spaces. The bin directory contains the executable programs. In these laboratory sessions you will use two of these, i.e.:

- MipsIt.exe: MipsIt Studio 2000 (MIPS programming environment).

- Mips.exe: MipsSim (MIPS simulator).

You will find further information about this platform in Annex I.

### Learning process and evaluation

**Pre-Lab work.** Some work must be completed before each session. Typically, you should read the documents for that session and answer the questions indicated as preliminary work. <u>This preliminary work will be evaluated during a brief interview with your lecturer at the beginning of the session. Students who are not yet members of a workgroup should complete this work individually. Later, during the laboratory class, they will be sorted into groups.</u>

**In-Lab work.** This component is evaluated in accordance with the work conducted in the lab. This work will be conducted in several stages with a range of activities weighted according to their complexity. On completion of each activity, students should call their lecturer to check that they have understood the task and completed it successfully. The lecturer can ask any task-related question to check whether the students has fully understood the problem and completed it in an original way. At the end of each laboratory session, students must also write up their answers to the questions posed during the session and hand these in to their lecturer.

**Post-Lab work.** For some laboratory sessions, students may also be required to prepare a short report. These reports may involve presenting tables or graphs of the measurements they have taken in the laboratory, providing justifications or theoretical explanations for those measurements, extending or generalizing some of the work they have completed, or completing several tasks in relation to the work they have carried out during the session. This report must be submitted before or at the beginning of the next laboratory session.

Student evaluation for each session will comprise the sum of the evaluations of their pre-lab work, laboratory work (typically between 2 and 3), and post-lab work (if applicable). Each component is evaluated with an A (Good), B (Regular) or C (Bad). The numerical value assigned to each letter depends on the number of stages. However, all A's awarded to students who have completed all the tasks well will be equivalent to a score of 9. A score of 10 is reserved for groups that have been awarded all A's for their laboratory session or have provided solutions of exceptional value and originality.

### 2. Preliminary (pre-lab) work

To make the most of your laboratory sessions you must complete all the following activities, spending the suggested amount of time on them. So as not to exceed the estimated maximum length of time suggested for each activity, all workgroup members must share the workload appropriately. If activities are not shared out appropriately or if any member tries to do too much work, the time available for other activities may be affected.

For their Pre-Lab work, all team members should read Annex I of this document, which describes the components of the MipsIt environment and explains how to work with it. It is important that you do this because it is your first contact with the software you will be working with in the next five laboratory sessions. You should also check certain ideas about the computer memory that you have studied so far. For some final questions, you will need to check some of the bibliographic sources shown or that are available on the Internet.

After reading Annex I, answer the following questions (these answers must be handed in at the beginning of the session):

- Q1. Briefly describe the elements that make up the computer implemented in the simulator.

- Q2. How many lines form the address bus of this microprocessor and how much memory can be addressed?

- Q3. Indicate the positions of the computer's main memory and explain which RAM technologies have been used in its implementation. Explain the differences between these two technologies.

- Q4. What kind of architecture (Von Neumann or Harvard) does the computer implement in the cache memory simulator?

- Q5. Explain which memory positions occupy all the Input/Output ports of the simulated computer.

- Q6. What is the size of the data we can read or write in the Input/Output ports?

- Q7. What are the positions from which an integer must be stored so that it is properly aligned in the simulator memory?

- Q8. What kind of data will always be aligned in C?

**First checkpoint:** Answers to Q1-Q8 must be written up and handed to the lecturer at the beginning of the session.

### 3. Lab (in-lab) work

In this session we will use MipsIt and check its functioning in a practical way with various programs that access its components. Answers to the questions must be written up and handed in at the end of the session.

3.1 To introduce students to the compiler and simulator, the C program below must be compiled and executed. To do so, the program (MipsIt.exe) must be executed. This program can be found in C:\Mipsit\bin. Just after the program begins, it may signal an error message related to ports that are not open, but the program will be executed normally. Initially, a project must be created (*Project* menu) with the option C(minimal)/Assembler. Files must not be saved in directories that contain spaces, accent marks or long names, so we recommended that you work in C:\tmp. Once there, you need to create a subdirectory with a suitable name, e.g. P1-1 (practice 1, part 1). In addition, a new C file associated with the project must be created with a ".c" extension. This should have the same name as the project: in this case, P1-1.c. The program code reads the value of the inputs and the position of I/O (input/output) 0xbf900000, and writes the read value on the same address, which shows this value in the LED bar.

```

#define TRUE 1

unsigned char *Switches = (char*) 0xbf900000;

unsigned char *leds = (char*) 0xbf900000;

int main ()

{

while (TRUE)

{

*leds=*Switches;

printf("The input value is: %X \n", *Switches);

}

}

```

The default compiler options must be edited whenever you wish to access the Input/Output space. These options remain linked to each project and are saved with it but, since they are not retained for the next project, they must be checked each time a new non-saved project is compiled. It is a good idea is to have a txt file open with the Notepad, from which you can copy the 2 boxes that must be edited (these appear in red below). The options to edit are in Project> Settings in the Link tab:

```

Base address: 0x80020000

Entry-point symbol: start

Libraries: kil,c,m,lnk,gcc,soft-float

Modules: crt0.o

Linker options: -Ttext 0x80020000 -e start -lkil -lc -lm -llnk -lgcc

-lsoft-float -N -nostdlib

```

- The project must be built in the compilation environment (F7). It should work, and the following messages should appear: Linking ... Post Build ... Done.

- Now the simulator should be opened (c:\Mipsit\bin\Mips.exe) and the code must be loaded into the simulator using the option Build>Upload>To Simulator (or F5). Once the code is loaded in the simulator, the name will appear in the upper part of the window P1-1.out.

- The program must be executed with the Cpu>Run simulator option or by pressing the button with the play symbol. A console will appear showing the printf message. To check the code works properly, the output input module must be opened with View>I/O. Now change the inputs associated with the input port through the switches. The LEDs must be activated with the pressed values. You must also check that the output value we have in the console matches the value entered by the switches.

- Q9. Why is the port pointer an unsigned char type?

- 3.2 In this new program, two integer data (32 bits) are accessed in memory locations 0x80020000 and 0xA0020000. A new project must be created (P1-2) with the explained methodology and with a new C code (P1-2.c). The program code will be:

```

#define TRUE 1

int *pos1 = (int*) 0x80020000;

int *pos2 = (int*) 0xA0020000;

int main ()

{

*pos2=0x000000000;

*pos1=0xf0f0f0f0;

printf("The memory 1 value is: %X \n",*pos1);

printf("The memory 2 value is: %X \n",*pos2);

while (TRUE);

}

```

- You need to build the project in the compilation environment and simulate it.

- Q10. Check the assembly code generated in the two previous examples and look when the CPU is accessing the I/O or the memory positions. What instruction is used to access the I/O positions? What instruction is used to access the memory positions in the MIPS? Is there any difference between these two types of access?

- Q11. How many bytes does an instruction have? How many memory positions does it occupy? In which kind of position does an instruction begin? Which kind of byte order (*Little-endian* or *Big-endian*) is used?

- 3.3 In this case, two integer variables are accessed in the memory positions 0x80020000 and 0x80020001. The program code is:

```

#define TRUE 1

int *pos1 = (int*) 0x80020001;

int *pos2 = (int*) 0x80020000;

int main ()

{

*pos2=0x000000000;

*pos1=0xf0f0f0f0;

printf("The memory 1 value is: %X \n",*pos1);

printf("The memory 2 value is: %X \n",*pos2);

while (TRUE);

}

```

- -You must build the project in the compilation software and simulate it.

- Does the program work properly? What problem do you think it has?

**Second checkpoint**: Call the lecturer and answer the questions in sections 3.2 and 3.3 or any other question related to these sections.

3.4 In this case, the entry position of the interrupts is accessed and its value is displayed.

```

#define TRUE 1

unsigned char *interrupt = (char*) 0xbfa00000;

int main ()

{

while (TRUE){

printf("The entry value is: %X \n", *interrupt);

}

}

```

The project must be built in the compilation software and be simulated.

The interrupt switches K1 and K2 must be pressed alternately. Then check and write down the values obtained by the entry position of the interrupts in each case. Discuss the results obtained by pressing the same switch several times.

3.5 You must implement a program in C code that read the inputs of the I/O module located in position 0xbf900000 associated with the switches. Accordingly, this value must turn ON the output LEDs as a level bar. The ranges of the input values with their corresponding output values are:

| Input     | Output                       |

|-----------|------------------------------|

| 0 - 31    | 1 (activates only 1st led)   |

| 32 - 63   | 2 (activates only 2nd led)   |

| 64 - 95   | 4 (activates only 3rd led)   |

| 96 -127   | 8 (activates only 4th led)   |

| 128 - 159 | 16 (activates only 5th led)  |

| 160 - 191 | 32 (activates only 6th led)  |

| 192 - 223 | 64 (activates only 7th led)  |

| 224 - 255 | 128 (activates only 8th led) |

Implement the program and simulate its correct functioning. Once you have finished, you must show the code to your lecturer.

**Third checkpoint**: Call the lecturer and answer the questions in sections 3.4 and 3.5 or any other question related to these sections.

The answers to Q1-Q11 must be written up and handed in to your lecturer.

### Annex I: MipsIt Studio 2000

### Introduction

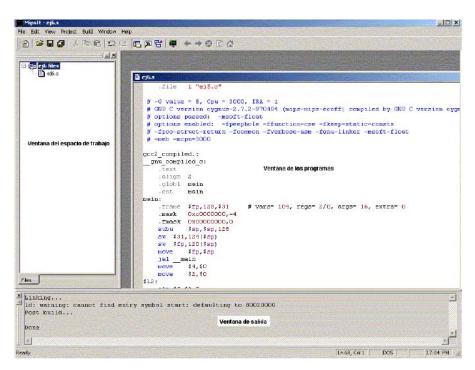

MipsIt is the software in which the programs for the first five practice sessions are written. The project is the basic concept for working in MipsIt Studio 2000. In this case this concept, already seen on previous programming and hardware design courses, can be understood as a set of interrelated source files that are compiled and linked to generate an executable file to be sent to the MIPS processor simulator. A MipsIt project can contain programs written in MIPS assembler, programs written in C language, and text files. In the programming interface we can see the following windows:

- The *Program window* shows the contents of the files.

- The Workspace window contains a list of all the files included in the project.

- The *Output window* provides information during the compilation and assembly phases.

MipsIt windows

### Configuration

In the File menu, Options sub-menu, you can configure MipsIt Studio 2000. Specifically, you can specify the directories in which to place the executable files (*bin*), the library files (*lib*) and the header files (*include*) for the application. You can also specify the location of the compiler (*bin/xgcc.exe*).

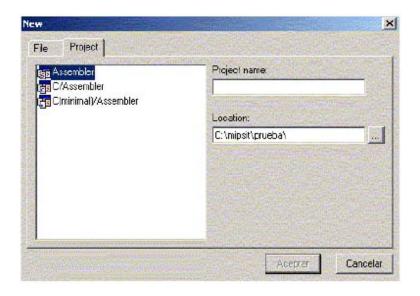

### How to create a new project

To create a project with MipsIt, you need to:

- 1. Select the *File -> New* menu. Click on *Project* if this is not selected by default.

- 2. Choose the type of project that will be created. There are three possibilities for this:

- a. Assembler: The project contains files only in assembler.

- b. *C/Assembler*: The project contains files only in C language or C files and assembly code. Programs with this option cannot be simulated with MipsSim.

- c. *C(minimal)/Assembler*: This is the same as in the previous case but only basic files of essential libraries are used. Programs with this option can be simulated with MipsSim.

- 3. The name of the project must be entered in *Project Name* and its location must be specified in *Location*.

- 4. Finally, click *Aceptar* in the window that appears below.

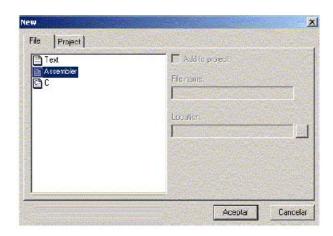

### How to add new files to a project

By following the previous steps, you have created an empty project without any file. To create files and add them to the project, follow the same steps as described earlier but in step 1 choose the *File* option.

Menu for creating a new project

### How to add existing files to a project

In this case, the *Add file* option is chosen within the Project menu. When the dialog box appears, select the file you wish to add to the project.

Menu for adding a new file to a project

### Compilation and assembly

If the *Build>Build* menu is chosen, all the files in C language will be compiled and all the project files will be assembled and linked. In the output window, information messages will appear about how the process has developed and whether there are any errors, etc. If you wish to recompile the whole project, you must choose the option *Rebuild All* from the *Build* menu.

### Assembly code generated by C programs

If any programs are written in C language, you can see the equivalent assembly program generated by MipsIt. To do so, once the program is compiled, the file written in C must be opened and the menu option Build->View Assembler must be selected.

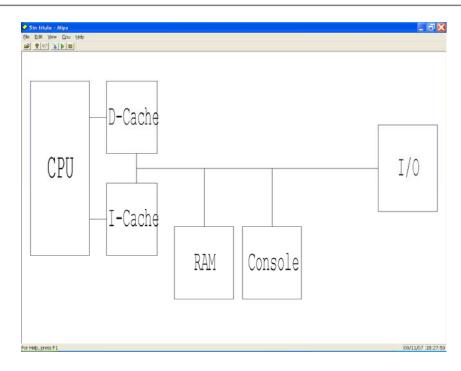

### **MipsSim: MIPS simulator (Mips.exe)**

### Introduction

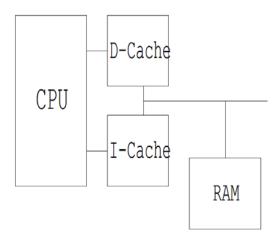

If a board with the MIPS processor is not available, a MIPS simulator is needed to check the functioning of the written programs. The MipsSim is a graphical environment that enables us to see the status of the memory, the CPU registers, the output console, etc., at any time during the execution of the program. Double-clicking on the Mips.exe file icon opens the following window with the modules:

- *CPU*: MIPS R2000 microprocessor.

- RAM Memory: Main memory.

- *Console*: Standard I/O.

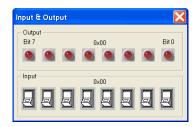

- *I/O*: I/O 8-bit port.

- *D-Cache and I-Cache*: Data and instructions separated cache memories.

Components of the MipsIt simulator

These modules can be opened by clicking on them. Below we describe in more detail the modules we will use in the laboratory sessions.

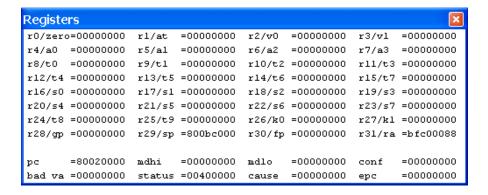

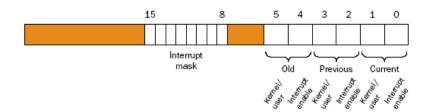

#### **CPU**

This enables us to view and modify the contents of the CPU registers, including the program counter (PC), the multiplication and division registers (HI and LO) (named mdhi and mdlo, respectively), and the registers of the coprocessor 0 (BAD VA, STATUS, CAUSE and EPC), which is responsible for controlling exceptions and virtual memory. Its visual appearance is as follows:

MIPS processor registers

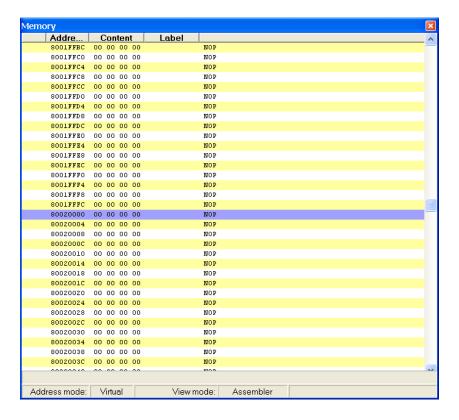

### **RAM** memory

Clicking on RAM opens a window with the contents of the memory ordered by rows. Each row has a specified address (*Address*) next to which the content of that address appears (*Content*). Both values appear in hexadecimal. If there is a label that identifies that instruction, it will appear in the column with the name: *Label*. The final column shows the equivalent assembly instruction for that code. Due to the use of pseudo-instructions, assembly instructions that appear in the memory may

not exactly match those that have been entered in MipsIt Studio 2000. Moreover, in some cases the assembly program may reorder the instructions for optimization purposes. Memory positions that do not have assigned data show their content with question marks.

The following diagram shows the structure of the RAM memory:

Content of some memory locations that can be addressed in the MIPS simulator

Since the MIPS memory contains 4GB, it is impractical to move along the memory using the arrows in the window or spacebar. It is better to use the contextual menu that appears if you click the right mouse button.

Options for navigating into the main memory

This menu has four sections:

1. The first section enables us to choose between displaying the virtual memory addresses (which can be addressed by the MIPS) or the physical memory (the one currently implemented).

- 2. The second section enables us to choose the display mode of the memory content for each instruction. By default, the *Assembler* option, which presents the memory content in assembler language, is used. We can also choose to display these values as if they are integers, unsigned integers, floating points or ASCII.

- 3. The third section enables us to move easily through the memory. The options are as follows:

- a. *Track PC*: This keeps the instruction indicated by the program counter (PC) in the centre of the window.

- b. *Jump to PC*: This jumps to the memory position indicated by the PC.

- c. Jump to SP: This jumps to the memory position indicated by the stack pointer.

- d. Jump to Symbol: This jumps to the memory position indicated by a label.

- 4. The fourth section enables to modify the value of the program counter by specifying the next instruction to be executed (Set Next Statement) and to establish a breakpoint for program-debugging tasks (Set Breakpoint). You can also establish breakpoints directly by double-clicking on the instruction of interest. The breakpoint is identified by a circle to the left of the instruction.

### Console

This provides the standard input/output for the programs. Here we can visualize the results of the program through the *printf* function.

Console of the MipsIt simulator

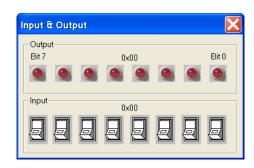

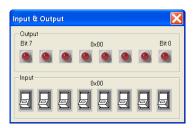

### I/O

This module simulates an 8-bit input/output unit. It includes 8 switches (inputs) and 8 LEDs (outputs). The value of the switches can be read when accessing position 0xBF900000 and the output value of the LEDs can be modified by writing also on this position.

8-bit Input/Output

### **Interrupts**

This simulates the interruption unit, with two interrupt buttons K1 and K2, and two timers. By enabling the external *Timer*, we can simulate the input of a periodic signal whose frequency can be modified with the control that appears below.

MIPS interrupts menu

### Load of an assembly program in the simulator

If both the MipsIt Studio 2000 and the MipsSim programs are open at the same time and a program is compiled with no errors, the assembler program of MipsIt Studio 2000 can be transferred to the simulator simply by choosing the menu option: *Build-> Upload-> To Simulator*. If the simulator is not open, an error window with the message 'Failed to upload to simulator' will appear when we try to perform this operation.

Another way to perform this operation is to select the *File-> Open* menu from the simulator. Then select the file with extension .srec or .out, which MipsIt Studio 2000 has created in the compilation and assembly phase of the project.

### **Program simulation**

If the program is already loaded in RAM, its functioning can be simulated. The following three buttons allow us to control the execution:

- Run: This allows the program to simulate the code completely (or until the first breakpoint). If the program has been stopped with the pause button (stop) or a break point, we can resume the execution.

- *Stop*: This enables us to pause the execution.

- *Step*: This enables us to execute the machine code instructions step by step.

### System memory map

Note that the system memory and the input I/O output devices share the same address space. With this kind of architecture, the instructions for reading and writing in the memory positions are the same as those used to read and write in the I/O devices.

The positions assigned to each component of the memory are:

0x80000000-0x800FFFFF 1MB SRAM (RAM static memory)

0xA0000000-0xA00FFFFF 1MB SRAM Uncached<sup>i</sup>, same physical memory as

0x80000000-0x800FFFFF

0x80400000-0x807FFFFF 4MB DRAM (RAM dynamic memory)

0xA0400000-0xA07FFFFF 4MB DRAM Uncached, same physical memory as

0x80400000-0x807FFFFF

0x80020000 Start address by default (default address where programs are

placed)

0xBF900000 Switches/LEDs (8-bit) 0xBFA00000 Interrupts I/O (8-bit)

Bit:

0 – K2 (Input): K2 instantaneous value. 1 – K1 (Input): K1 instantaneous value.

2 – Timer (Input): Timer instantaneous value.

3 - N/A (undefined)

4 – K2 latch: Captured value of K2 upon interruption. This must

be reset by the user.

5 – K1 latch: Captured value of K1 upon interruption. This must

be reset by the user.

6 – Timer latch: Captured value of the Timer. This must be reset

by the user.

7 - N/A (undefined)

0xBFB00000 16-bit I/O (not implemented in the MipsSim simulator)

<sup>i</sup> The Uncached memory positions are the same as the reference memory positions, so the physical memory is the same. The difference is that when these positions are accessed, access is made directly to memory and the content of the cache memory is not modified (data are not stored in the cache memory).

MipsIt Introduction Page 14

-

Lab 2

# Laboratory 2: Cache Memory (part I)

(Updated at 29/01/2019)

Work at home (planned) time: 1:30 h

Lab time: 2:30 h

### 1. Introduction

In this second laboratory session we will study the cache memory system and see how it functions when simple programs are executed with regular access patterns to memory. Cache memory performance will be studied while taking into account the mapping algorithm used. We will also analyse several techniques for making programs more efficient. These techniques can significantly reduce the failure rate when a system is run with cache memory.

We begin with a description of the MIPS cache memory and the configuration options that are possible in the MipsIt Simulator. We will then use a simple program to show the process involved in compiling and adapting the code to ensure that the experiments we carry out are performed correctly. We will then conduct several experiments in which the characteristics of the cache memory are modified.

### Goals

On completion of this laboratory session you will be able to:

- understand the possible configurations of the MipsIt cache system,

- configure the cache memory module of the MipsIt simulator,

- adapt a C program to evaluate the use of the cache memory in the MipsIt,

- evaluate the use of the cache memory for a simple program, and

- determine the causes of the cache behaviour from the access patterns.

### 2. Preliminary (pre-lab) work

For pre-lab work, all members of the laboratory groups should read Annex I of this document, which describes the cache memory module for the MipsIt simulator. You should also read Annex II, which describes the steps to follow to adapt the example program we use in the laboratory to check the functioning of the cache memory. You also ned to review the concepts on computer memory that were explained in Topic 1. For some questions you must consult some of the bibliographic sources indicated or that are available on the Internet.

After reading Annex I and II, answer the following questions:

- 1. What kind of architecture (Von Neumann or Harvard) is used in the simulated computer, both for the cache memory system and the main memory system?

- 2. Explain the meaning of the following cache memory configuration parameters: *Size*, *Block Size* and *Block in sets*.

- 3. Indicate the number of memory positions occupied by each element of the matrices described in the C program shown in Annex II. What characteristic must all starting positions of the matrix elements have? How many positions separate the beginning of two contiguous elements of the matrices?

- 4. Explain whether the contiguous elements (which occupy consecutive positions) in the example program are elements of the same row or the same column.

- 5. What is the total size (in bytes) of the matrices in the memory?

- 6. In the example program, the loops are used to access matrices m1 and m2. Is the matrix read by rows or by columns? Specify whether in each iteration of the internal loop the next elements of the matrices are in contiguous memory positions.

- 7. Indicate which instructions of the assembly code in the assembler program of Annex II, obtained as a result of the compilation of the C code perform, enable access to the positions of the matrices (reading of m1[i][j] and writing of m2[i][j]).

**First checkpoint:** Answers to the pre-lab questions must be written up and handed in to the lecturer at the beginning of the session. Any questions posed by the lecturer on these or related issues must be answered in the same way.

### 3. Lab (in-lab) work

In this session we will check the behaviour of the MipsIt cache memory for several programs and configurations in a practical way.

3.1 Use the example program in Annex II, with the assembly code modified, and configure the Data Cache (D-Cache) with the following characteristics:

Size: 16Size block: 4

• With postponed writing (write-back).

Replacement: LRU

- The sequence of accesses (memory addresses expressed in hexadecimal) the program performs on the memory when accessing the m1 and m2 variables must be written up. To do this, fill in the attached table. The range of memory positions occupied by each of these variables expressed in hexadecimal must also be written in the table.

**Note:** To determine which addresses are occupied by these variables, the program must be executed step by step or, alternatively, set a breakpoint and check the addresses accessed on the data memory when reading variable m1 and writing on m2, respectively (the address appears in the cache data window two cycles after the instruction has been executed).

| Access number | i | j | m1 address | m2 address |

|---------------|---|---|------------|------------|

|               |   |   |            |            |

| 1             |   |   |            |            |

| 2             |   |   |            |            |

|               |   |   |            |            |

| 15            |   |   |            |            |

| 16            |   |   |            |            |

### **Computer Structure Laboratory**

- Also complete the table below to explain which bits are used for the tag, which bits are used as an index, which are the word selection bits, and which bits are used to select the byte in a line.

| Mapping algorithm                           | Tag bits | Index bits | Word bits | Byte bits |

|---------------------------------------------|----------|------------|-----------|-----------|

| Direct (Blocks in set= 1)                   |          |            |           |           |

| K-way associative: 2 ways (Blocks in set=2) |          |            |           |           |

| Fully associative (Blocks in set=4)         |          |            |           |           |

- Perform several simulations with the mapping algorithms shown in the table below. Then complete the table with the total number of misses and the miss rate obtained from these simulations:

| Mapping algorithm                           | Number of misses | Miss rate |

|---------------------------------------------|------------------|-----------|

| Direct (Blocks in set= 1)                   |                  |           |

| K-way associative: 2 ways (Blocks in set=2) |                  |           |

| Fully associative (Blocks in set=4)         |                  |           |

**Second checkpoint**: Call the lecturer, show them the tables, and answer any questions on their content.

3.2 Now the program will be modified to improve its performance. In this case, the program exchanges the loops that are used to read/write the matrices. The aim is that the matrix should be accessed in the same order in which it is stored in the memory and so the proximity of the program's spatial references will be increased. To do so, the loops are modified as follows:

```

#define NUM1 4

int main()

{

register int i,j;

int m1[NUM1][NUM1];

int m2[NUM1][NUM1];

for(i=0;i<NUM1;i++)

for(j=0;j<NUM1;j++)

m2[i][j]=m1[i][j];

}</pre>

```

- The program must be compiled to obtain the assembly code, eliminate the remaining lines, and the same modifications should be made as in the previous section. Once the executable final code has been obtained, it must be loaded into the simulator. Simulations must then be repeated for the same types of data caches, as in the previous case.

- The sequence of accesses to memory performed when variables m1 and m2 are accessed must be monitored. To do so, complete a table as in 3.1.

- The following table must also be completed with the total number of misses and the miss rate obtained from the simulations:

| Mapping algorithm                           | Number of misses | Miss rate |

|---------------------------------------------|------------------|-----------|

| Direct (Blocks in set= 1)                   |                  |           |

| K-way associative: 2 ways (Blocks in set=2) |                  |           |

| Fully associative (Blocks in set=4)         |                  |           |

Which mapping algorithms are more suitable for this algorithm?

- 3.3 After obtaining the experimental data, answer the following questions with reasoned arguments:

- Explain why the failure rate for the second algorithm decreases in comparison with the first algorithm. Hint: to discover why this technique works better, compare the access pattern and the state of the cache memory after each iteration of the loops.

- Does any mapping algorithm not improve its failure rate for the second algorithm? Explain why. Hint: check which line of the cache memory is assigned to the blocks of different matrices in the same iteration of the loop.

- The simulation must be repeated with 2-way associative mapping using the following program:

Write down the results, compare them against the original algorithm, and suggest an explanation for this behaviour. The program simulation must be repeated with a random replacement algorithm instead of LRU. Does this change anything? Why (not)?

**Third checkpoint**: Call the instructor and show the results of points 3.2 and 3.3. Answer any questions on these results.

### Annex I: MipsIt cache module

### Introduction

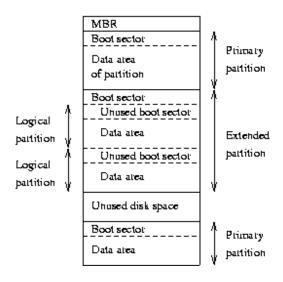

The MIPS microprocessor cache has a Harvard architecture with independent instructions memory (I-Cache) and data memory (D-Cache), though the main memory follows a Von Neumann architecture.

MIPS memory hierarchy.

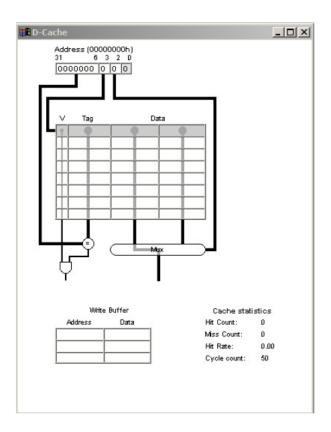

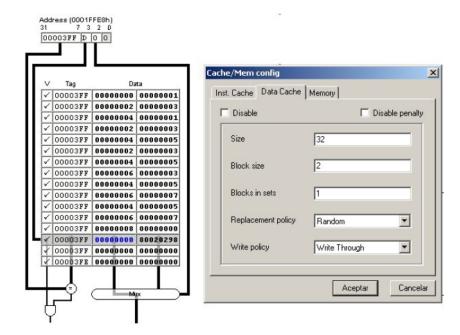

The following figure shows the contents of the data cache memory (D-Cache) when clicking on the module in the MipsIt simulator. This information is similar for the instruction cache module (I-Cache).

Contents of the D-Cache memory of the Simulator

This scheme comprises four parts:

- Current address (*Address*): This is divided into the following fields: *Tag*, *Line* or set and *Word*. The structure changes depending on the configuration of the cache memory. In the above scheme:

- o *Tag*: Bits 6 to 31.

- o *Line*: Bits 3 to 5.

- o *Word*: This corresponds to the last two fields (bits from 0 to 2). Since 4-byte words are stored in the cache and the processor can address at the byte level, the two least significant bits (0 and 1) identify a byte within the word but are irrelevant for accessing the cache. The other bits of the word field refer to the 4-byte words that form each line. In this case, bit 2 identifies the two 4-byte words that form each line.

- The Cache itself: The selected line (based on the line or set field) appears in grey. The word selected by the word field appears in blue. The V column indicates whether that line is valid. For a cache with a delayed write (write back, WB), an extra column appears. This column indicates whether the line coincides with the main memory (D, dirty).

- Write Buffer: This appears if the size of the buffer is non-zero. It can be configured for both direct (WT) and delayed (WB) writing.

- Cache statistics: This part shows the number of hits in the cache module (hit count), the number of misses in the cache module (miss count), and the percentage of hits (hit rate).

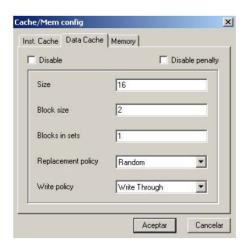

### **Cache configuration**

To configure the cache memory, choose the option:

*Edit*→*Cache/MemConfig*. The following window appears:

Cache configuration menu

From this menu we can choose the data and instruction cache configurations. The following options appear in the data cache:

- *Size*: Cache size in words.

- *Block Size*: Number of words in each block.

- *Block in sets*: Associativity degree (number of ways in each set).

Note that

- o the word always has 4 bytes,

- o Size/Block Size = the number of lines in the cache module,

- o the number of lines can be grouped into sets, and

- o block in sets identifies the number of lines (ways) per set.

- Replacement policy: Three techniques (policies) to replace the lines are implemented (RANDOM, FIFO or LRU).

- Write policy: One of two writing techniques (Write Back or Write Through) must be chosen.

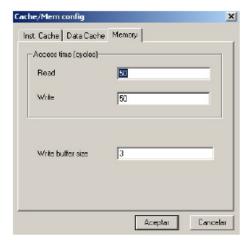

The cache memory can be deactivated by selecting the *Disable* button. You can also disable the penalty incurred by a miss in the cache memory by activating the *Disable penalty* button. The configuration of the Instruction Cache (I-Cache) is similar except that the *Write policy* option does not appear. The memory configuration window is shown in the following figure:

Configuration of the access penalty to main memory

This menu specifies the cycles that penalize cache misses in the read and write operations, as well as the *write buffer size*. You can also view the statistics for the cache memory from the option  $View \rightarrow I$  Cache Stats or D Cache Stats (for the instructions and data cache, respectively). Here are some examples of cache configurations.

### Configuration example 1.

In this example, the data cache memory has the following features:

- Total size (Size): 32 words of 4 bytes; 128 bytes in total.

- Line size: 2 words on each line (Block size = 2); 8 bytes on each line in total.

- Direct Mapping (Block in sets = 1). In other words, each set has a line (Associativity of 1).

Based on the configuration of the cache memory described, the main memory address comprises the following fields:

- Tag: bits from 7 to 31.

- Line: bits from 3 to 6 (16 lines = Size/Block size = 128/8).

- Word: 2 words (bit 2) of 4 bytes each (bits 0 and 1). Addressable at byte level.

In addition, the replacement technique is random (RANDOM), though with direct mapping it has no influence on its operation, and the writing policy is WT.

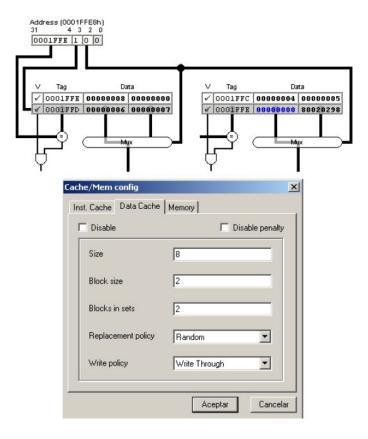

### **Configuration example 2**

In this example, a data cache memory is shown with the following characteristics:

- Total size: 8 words of 4 bytes; 32 bytes in total.

- Line size: 2 words on each line (block size = 2); 8 bytes on each line in total.

- 2-associative mapping (block in sets = 2).

Based on the configuration of the cache memory, the main memory address has the following fields:

- Tag: bits from 4 to 31.

- Set: bit 3 (2 sets).

- Word: 2 words (bit 2) of 4 bytes each (bits 0 and 1). Addressable at byte level.

In addition, the replacement technique is random (RANDOM) and the writing policy is WT.

### Annex II: Example code

### Introduction

This annex describes the modifications we will make to the programs we use in this and the next laboratory class to properly analyse the behaviour of the cache memory. To do so, the programs will be done in C. They will then need to be compiled, and the assembler generated by the compiler will need to be edited to eliminate any extra instructions that do not follow the pattern for the algorithm. In this way, we will only be able to execute the code for the algorithm we are interested in

### **Code to analyse:**

In this session we will study the following example program written in C language:

```

#define NUM1 4

int main()

{

register int i,j;

int m1[NUM1][NUM1];

int m2[NUM1][NUM1];

for(j=0;j<NUM1;j++)

for(i=0;i<NUM1;i++)

m2[i][j]=m1[i][j];

}</pre>

```

In this session we will obtain the miss rate of the data cache when executing the program shown earlier. This program assigns two matrices: m2=m1. The example program (p3.c) must be compiled in the Mipsit environment. The result of this compilation is an assembly file that we can visualize with the  $Buil \rightarrow View$  Assembler option. This file contains the following code:

```

.file

1 "p3.c"

\# -G value = 8, Cpu = 3000, ISA = 1

# GNU C version cygnus-2.7.2-970404 (mips-mips-ecoff) compiled by GNU C version cygnus-2.7.2-

970404.

# options passed: -msoft-float

# options enabled: -fpeephole -ffunction-cse -fkeep-static-consts

# -fpcc-struct-return -fcommon -fverbose-asm -fgnu-linker -msoft-float

# -meb -mcpu=3000

gcc2_compiled.:

__gnu_compiled_c:

.text

.align

.globl main

# Change main by start

# Change main by start

.ent

main

main:

# Change main by start

.frame $fp,216,$31

# Delete these lines

.mask 0xc0000000,-4

.fmask 0x00000000,0

subu $sp,$sp,216

SW

$31,212($sp)

SW

$fp,208($sp)

move $fp,$sp

ial

main

```

```

move

$3,$0

$L2:

slt

$4,$3,4

bne

$4,$0,$L5

$L3

$L5:

noreorder

.set

nop

.set

reorder

$2,$0

move

$L6:

slt

$4,$2,4

$4,$0,$L9

bne

$L4

j

$L9:

$4,$2

move

$5,$4,4

addu

$4,$fp,16

addu

$5,$5,$4

addu

$4,$5,128

move

$5,$3

sll

$6,$5,2

addu

$4,$6,$4

move

$5,$2

sll

$6,$5,4

$7,$fp,16

addu

addu

$5,$6,$7

move

$6,$3

sll

$7,$6,2

addu

$5,$7,$5

move

$6,$2

sll

$7,$6,4

addu

$6,$fp,16

addu

$7,$7,$6

addu

$6,$7,64

move

$7,$3

sll

$8,$7,2

addu

$6,$8,$6

lw

$5,0($5)

lw

$6,0($6)

addu

$5,$5,$6

sw

$5,0($4)

$L8:

$2,$2,1

addu

$L6

$L7:

$L4:

addu

$3,$3,1

$L2

$L3:

$L1:

move

$sp,$fp

# Delete these lines

lw

$31,212($sp)

$fp,208($sp)

lw

addu

$sp,$sp,216

# This line has not to be deleted, but

#$31 has to be changed by $L1

.end

main

# Change main by start

```

To simplify the simulation of the program execution, the lines of the assembly code that are in bold and italic must be eliminated. By doing this, it is possible to execute only the code resulting

from the 2 loops and eliminate extra access to the memory that we do not want in our code. The lines we eliminate are designed for the call to the main () function of C and involve storing and retrieving information in the MIPS data stack stored in the memory. These accesses therefore imply changes to both the data cache and the instructions cache.

We must also change the references to the **main** tag by the **start** tag. The programs in the simulator are launched from the address labelled *start*, which by default performs a jump to the *main* tag, so that the assembler code can be executed without any problem.

The resulting file is as follows:

```

.file

1 "p3.c"

# -G value = 8, Cpu = 3000, ISA = 1

# GNU C version cygnus-2.7.2-970404 (mips-mips-ecoff) compiled by GNU C version cygnus-2.7.2-

# options passed: -msoft-float

# options enabled: -fpeephole -ffunction-cse -fkeep-static-consts

# -fpcc-struct-return -fcommon -fverbose-asm -fgnu-linker -msoft-float

# -meb -mcpu=3000

gcc2_compiled.:

_gnu_compiled_c:

.text

2

.align

.globl

start

.ent

start

start:

move

$3,$0

for(j=0;j<NUM1;j++)</pre>

$L2:

#

slt

$4,$3,4

bne

$4,$0,$L5

$L3

$L5:

.set

noreorder

nop

.set

reorder

move

$2,$0

$L6:

#

for(i=0;i<NUM1;i++)</pre>

slt

$4,$2,4

bne

$4,$0,$L9

$L4

$L9:

move

$4,$2

#

sll

$5,$4,4

addu

$4,$fp,16

addu

$5,$5,$4

addu

$4,$5,128

move

$5,$3

sll

$6,$5,2

addu

$4,$6,$4

move

$5,$2

sll

$6,$5,4

addu

$7,$fp,16

$5,$6,$7

addu

move

$6,$3

sll

$7,$6,2

$5,$7,$5

addu

move

$6,$2

sll

$7,$6,4

addu

$6,$fp,16

addu

$7,$7,$6

```

### **Computer Structure Laboratory**

```

addu

$6,$7,64

move

$7,$3

sll

$8,$7,2

$6,$8,$6

addu

lw

$5,0($5)

$5,0($4)

SW

$L8:

addu

$2,$2,1

$L6

$L7:

$L4:

addu

$3,$3,1

$L2

$L3:

$L1:

$L1

.end

start

```

Finally, the file must be saved under, for example, the name P3.S, and a new assembly-type project containing only this file must be created. The new project must be compiled within MipsIt and loaded in the simulator. At this time, it is possible to simulate the behaviour of the code for the cache configuration that has been chosen.

Lab 3

## Laboratory 3: Cache Memory (part II):

### **Software Optimizations**

(Updated at 29/01/2019)

Work at home (planned) time: 1:30 h

Lab time: 2:30 h

### 1. Introduction

In this laboratory session we will study the cache memory system and its behaviour by optimizing simple algorithms related to typical access patterns in numerous applications. The behaviour of the cache memory will be studied depending on the mapping algorithm used. We also explain how the system responds to the various optimization techniques.

In the previous laboratory class, we studied an example of software optimization on an algorithm that added two matrices. The example showed how the miss rate was affected exchanging the loops that are used to read and write the matrices.

It is important to establish a workgroup dynamic that enables you to take maximum profit from your time in the laboratory. For this reason, you should arrive at the laboratory on time and pay attention to your lecturer's instructions.

### Goals

On completion of this session you will be able to

- understand the software optimization techniques that enable the cache memory to perform better,

- evaluate the behaviour of the most common optimization techniques for different configurations of the cache memory,

- apply software optimization techniques to their algorithms, and

- predict how the cache memory will function with the proposed algorithms before applying the proposed optimizations techniques.

### **Materials**

We will use the same software as in the two previous laboratory sessions (P1 and P2).

### 2. Preliminary (pre-lab) work

For the pre-lab work for this session, all members of the workgroups must read Annex I of this document, which describes the most common software optimization techniques for extracting the greatest benefit from the cache system. You should also review the main concepts of memory we have studied in class so far.

After reading Annex I and reviewing the memory subject, answer the following questions:

- 1. What do the techniques that modify access to the data try to improve?

- 2. What do the techniques that modify the data layout try to improve?

- 3. Explain which optimization technique is used in the algorithm in the following example:

```

//Original algorithm

//Modified algorithm

#define N 16

#define N 16

int main()

int main()

register int i,j,suma;

register int k,l,suma;

int m[N][N];

int m[N][N];

for(j=0;j<N;j++)</pre>

for(k=0;k<N;k++)

for(i=0;i<N;i++)</pre>

for(1=0;1<N;1++)

suma+=m[i][j];

suma= suma + m[k][1];

```

4. Explain in which situations the modified algorithm does not improve the miss rate if we have a cache with direct mapping.

5. Explain which optimization technique is used in the algorithm in the following example:

```

//Original algorithm

//Modified algorithm

#define N 16

#define N1 16

#define N2 17

int main()

int main()

register int i,j,suma;

int m1[N][N];

register int i,j,suma;

int m1[N1][N2];

int m2[N][N];

for(j=0;j<N;j++)

int m2[N1][N2];

for(i=0;i<N;i++)

for(j=0;j<N1;j++){

suma=m1[j][i]+m2[j][i];

for(i=0;i<N1;i++)

}

suma= m1[j][i]+ m2[j][i];

```

- 6. Which kind of cache benefits the most from the type of optimization in Q5 above?

- 7. Which kind of cache would benefit the most from the array merging technique?

### 3. Lab (in-lab) work

In this laboratory session, we will check, in a practical way, the behaviour of the cache memory after several optimizations have been applied to the algorithm we used in the previous session. You must therefore bring to this laboratory session a copy of the results you obtained in that one.

3.1 Using the matrix addition algorithm shown below, modify the algorithm using the array padding technique.

The program must be compiled to obtain the assembly code. Then edit this code to eliminate several lines and change some labels as we did in the previous laboratory session. When the code is ready, upload it to the simulator. The data cache must also be configured with the following parameters:

- Size: 16

- Block size: 4

- With delayed writing (write-back)

- Replacement algorithm: LRU

- Indicate the sequence of accesses (memory addresses expressed in hexadecimal) the program performs on the memory when it accesses variables m1, m2, m3 and m4. To do so, fill in the table below. Also indicate (in hexadecimal) the range of memory positions occupied by each of these variables.

| Access<br>number | i | j | m1 address | m2 address | m3 address | m4 address |

|------------------|---|---|------------|------------|------------|------------|

| 1                |   |   |            |            |            |            |

| 2                |   |   |            |            |            |            |

|                  |   |   |            | •••        |            |            |

| 15               |   |   |            |            |            |            |

| 16               |   |   |            |            |            |            |

- Several simulations with cache memories with different mapping algorithms should be performed to complete the following table with the total number of misses and the miss rate obtained from

### **Computer Structure Laboratory**

the simulations for the two algorithms (the original one and the algorithm improved with array padding):

| Mapping algorithm            | Number of misses | Miss rate |

|------------------------------|------------------|-----------|

| Direct (Blocks in set= 1)    |                  |           |

| K-way associative: 2 ways    |                  |           |

| (Blocks in set=2)            |                  |           |

| Fully associative (Blocks in |                  |           |

| set=4)                       |                  |           |

- The results must be compared and understood for each mapping algorithm. The original algorithm must be compared to the one improved by array padding.

- Using the same original algorithm, the replacement algorithm of the cache memory must be changed to Random. Several simulations must be performed to complete the following table with the total number of misses and the miss rate obtained by the simulations:

| Mapping algorithm                           | Number of misses | Miss rate |

|---------------------------------------------|------------------|-----------|

| K-way associative: 2 ways (Blocks in set=2) |                  |           |

| Fully associative (Blocks in set=4)         |                  |           |

8. Explain the differences obtained in both cases (LRU and Random).

First checkpoint: Call the lecturer, show them the tables, and answer any questions on their content.

- 3.2 In this second section, the original program must be modified using the **array merging** technique. The code execution must be simulated by following the same steps as in section 3.1.

- Indicate the sequence of accesses: memory addresses expressed in hexadecimal that the program performs on the memory when accessing variables m[][].m1, m[][].m2, m[][].m3 and m[][].m4. To do so, complete the attached table. Similarly, write down the range of memory positions occupied by each of these variables, expressed in hexadecimal.

| Access<br>number | i | j | .m1 address | .m2 address | .m3 address | .m4 address |

|------------------|---|---|-------------|-------------|-------------|-------------|

| 1                |   |   |             |             |             |             |

| 2                |   |   |             |             |             |             |

|                  |   |   |             |             |             |             |

| 15               |   |   |             |             |             |             |

| 16               |   |   |             |             |             |             |

### **Computer Structure Laboratory**

- Perform simulations with caches with different mapping algorithms using the configuration of the cache memory proposed in the previous section. Complete the following table with the total number of misses and the miss rate obtained by the simulations:

| Mapping algorithm                           | Number of misses | Miss rate |

|---------------------------------------------|------------------|-----------|

| Direct (Blocks in set= 1)                   |                  |           |

| K-way associative: 2 ways (Blocks in set=2) |                  |           |

| Fully associative (Blocks in set=4)         |                  |           |

- 9. Compare and explain the results obtained with different cache mapping algorithms, the original algorithm, and the algorithm modified with array merging.

- 10. Does the replacement algorithm (LRU or Random) have any effect? To determine this, you need to perform simulations with these replacement algorithms.

**Second checkpoint**: Call the lecturer, show them the tables, and answer any questions on their content.

Answers to the preliminary questions (1 to 7) and questions 8, 9 and 10 must be written up and handed in to the lecturer before you leave the laboratory.

## Annex I: Basic techniques of software optimization

### Introduction

The memory hierarchy enables us to hide both the low bandwidth and the latency of the main memory, which are slow in comparison with current CPUs. For this reason, the cache memory located between the main memory and the CPU is used. Unfortunately, as the cache size is limited, it only stores copies of recently used data. Normally, when new data are loaded into the cache memory, older data must be replaced.

Cache memory reduces the program execution time because a program follows the principle of locality. We must therefore design algorithms that follow both spatial and temporal localities. In this document we will present several basic techniques that will help us to design algorithms that improve cache memory utilization.

These techniques will be based on transforming the original algorithm. The idea is to modify the data access arrangement or the data storage itself in order to improve the locality of temporal and spatial reference. Below we describe some of the most useful techniques.

### **Data access optimizations**

The aim of data access optimizations is to improve the locality of data. For this, modifications are made to the loops of the algorithms, which are often nested, so that at each iteration data used in the preceding iterations are reused or, similarly, data close to the used ones, which have been copied in the cache in immediately preceding iterations, are accessed.

We now present a set of transformations aimed at improving spatial locality for a cache level (L1) in the memory hierarchy.

### Loop interchange

Using this technique, the program is modified to improve its performance. In this case, the program exchanges the loops that are used to go through the matrices. The aim is for the matrix be accessed in the same order in which it is stored in the memory, thus increasing the spatial proximity of the references in the program. This technique can only be used if the order of the loops is not important.

When the loop interchange technique is generalized to more than two loops, it is called loop permutation. In this case, two loops of the algorithm can be exchanged without being adjacent.

To illustrate this technique, we will use a matrix addition example. In this algorithm, all the elements of two matrices (m1 and m2) are read and added, and the result obtained is assigned to a third matrix (m3). The sentence is as follows:

We must go through the rows and columns of the matrices to access their elements. However, the elements of a matrix are stored in the memory following an order of consecutive rows (C code) or columns (Fortran code). In the case of C language, the element m[i][j+1] of a matrix is next to the element m[i][j], while the element m [i+1][j] is a row away from m[i][j] (i.e. N positions away, where N is the number of elements in a row).

Below (left) is the original version of the previous algorithm, where the inner loop accesses elements of different rows each time, which implies low reference locality.

```

Loop interchange

// Original nested loops

//Modified nested loops

#define N 4

#define N 4

int main()

int main()

register int i,j;

register int i,j;

int m1[N][N];

int m1[N][N];

int m2[N][N];

int m2[N][N];

int m3[N][N];

int m3[N][N];

for(j=0;j<N;j++)

for(i=0;i<N;i++)

for(i=0;i<N;i++)

for(j=0;j<N;j++)

m3[i][j]=m1[i][j]+m2[i][j];

m3[i][j]=m1[i][j]+m2[i][j];

```

However, on the right, the accesses at each iteration are done with elements of the same row until the row ends. This increases spatial locality and, therefore, use of the cache memory.

### Loop fusion

Loop fusion involves a transformation that takes two adjacent loops that have the same cross-sectional iteration space. This transformation combines their bodies in a single loop. The merge can be performed if there are no dependencies between the loops, i.e. if the instructions in the first loop do not affect the instructions in the second loop. By merging two loops we reduce the additional cost of the instructions that implement the loops, increase temporary locality, and increase the performance of the processor with a greater number of instructions per iteration, thus reducing the number of accesses to memory.

To illustrate this technique, we will use an example of the sum of two vectors with previous scaling. In this algorithm all the elements of a vector (v1) are scaled, first by scaling them with a value (a), then adding each element of the vectors (v1 and v2) and assigning the result to a third vector (v3). The sentence that is repeated is:

```

v1[i]= v1[i]*a;

v3[i]= v1[i]+v2[i];

```

If two loops are used, we must first go through the whole vector v1 to scale it. Then, when we start the second loop, we must access the elements of v1 again. After loop fusion you must access the elements of v1 only once.

Below (left) shows the example of the previous algorithm in its original version where two loops are used, one to scale vector v1 and one to add the vectors, which implies low reference locality.

```

Loop fusion

// Original code

// Modified code with loop fusion

#define N 4

#define N 4

int main()

int main()

register int i, a;

register int i,a;

int v1[N], v2[N]v3[N];

int v1[N], v2[N]v3[N];

for(i=0;i<N;i++)

for(i=0;i<N;i++){

v1[i]= v1[i]*a;

v1[i]= v1[i]*a;

for(i=0;i<N;i++)</pre>

v3[i] = v1[i] + v2[i];

v3[i] = v1[i] + v2[i];

```

However, when both loops are merged in the implementation on the right, the computed v1 element is immediately reused and added to vector v2. This strategy increases temporary locality and, therefore, use of the cache memory.

### **Data layout optimizations**

In the previous section we saw how the program's data locality can be improved by rearranging access to the data. However, in many applications, the transformation of the loops is not sufficient to obtain good data locality, especially when there is a high degree of conflict misses.

Data layout optimizations modify how data structures and variables are arranged in memory. These transformations aim to avoid effects such as cache conflict misses and false sharing to improve the spatial locality of the data.

### Array padding

When several arrays are accessed sequentially, the accesses may generate conflict misses systematically due to the dimensions of the arrays and the cache memory. A typical example of this was shown in the program in the previous lab session, where the direct and K-way associative mappings produced conflict misses systematically because the size of the arrays coincided with the size of the cache memory. This situation commonly appears when the data are stored in blocks whose sizes are a multiple of the cache size.

In the example of the sum of matrices, therefore, all accesses to the matrices are made on blocks assigned to the same lines or sets in the cache memory, thus producing conflict misses and making it impossible to reuse the blocks between several iterations of the internal loop (access within the same row).

This problem can be solved by array padding. With this technique, the size of the array is increased, for example by increasing the number of columns or rows and, therefore, the number of elements in the array. These new elements are not used in the iterations of the algorithm because they are not needed – they are only introduced to avoid conflict misses in the access between different matrices.

Below (left) shows the example of the sum of the matrices in its original version, where the elements m1[i][j], m2[i][j] and m3[i][j] are separated with a multiple of the size of the cache memory. This can lead to conflicts in the occupation of the cache and, therefore, misses, which implies low reference locality.

```

Array padding

//Original code

//Modified code with array padding

#define N 4

#define N1 4

#define N2 5

int main()

int main()

register int i,j;

int m1[N][N];

register int i,j;

int m2[N][N];

int m1[N1][N2];

int m3[N][N];

int m2[N1][N2];

for(i=0;i<N;i++)

int m3[N1][N2];

for(j=0;j<N;j++)

for(i=0;i<N1;i++)

m3[i][j]=m1[i][j]+m2[i][j];

for(j=0;j<N1;j++)

}

m3[i][j]=m1[i][j]+m2[i][j];

```

In the implementation on the right, however, when the matrices are filled with a column element, the elements of matrices m1[i][j], m2[i][j] and m3[i][j] avoid matching the same block of the cache memory.

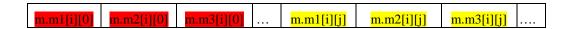

### Array merging

This optimization technique can be used when the program refers to several arrays of the same dimension and the same indexes are used. This technique avoids the problem described in the previous case (it reduces the number of conflict misses) but without unnecessarily increasing array size. The array merging technique involves combining these independent arrays in a composite array.

This technique can be used to improve spatial locality. It is best applied if elements of different arrays are located far away in the memory but must be accessed together. The original arrangement in the memory of the three elements of the matrices to be added is therefore:

After the arrays are combined, the situation of the elements is:

Below is the original code for the algorithm of the sum of matrices (left) and the code modified through array merging (right).

```

Array merging

// Original code

//Array merging code

#define N 4

#define N 4

int main()

int main()

register int i,j;

register int i,j;

int m1[N][N];

struct mezcla{ int m1;

int m2;

int m2[N][N];

int m3[N][N];

int m3;

for(i=0;i<N;i++)</pre>

for(j=0;j<N;j++)

struct mezcla m[N][N];

m3[i][j]=m1[i][j]+m2[i][j];

for(i=0;i<N;i++)</pre>

}

for(j=0;j<N;j++)</pre>

m[i][j].m3=m[i][j].m1+m[i][j].m2;

```

#### Reference

M. Kowarschik and C. Weib, "An Overview of Cache Optimization Techniques and Cache-Aware Numerical Algorithms", Algorithms for Memory Hierarchies. Lecture Notes in Computer Science (Springer Berlin / Heidelberg), Vol. 2625, pp. 213-232, 2003. (Online in: <a href="http://citeseer.ist.psu.edu/viewdoc/summary?doi=10.1.1.8.7904">http://citeseer.ist.psu.edu/viewdoc/summary?doi=10.1.1.8.7904</a>).

Lab 4

# Laboratory 4: Input/Output System (I):

## **Polling (Software-driven I/O)**

(Updated at 29/01/2019)

Work at home (planned) time: 1:30 h

Lab time: 2:30 h

## 1. Introduction

In this laboratory session we will study the computer input/output system and the synchronization technique of peripheral devices based on polling, also called software-driven I/O. This will enable us to also study how to access the status information of peripheral devices.

#### Goals

On completion of this session you will be able to:

- understand techniques for checking and modifying the status information of a peripheral,

- design algorithms to check the value of the status bits of a peripheral and respond accordingly,

- use bitwise operators (in C code) to check and modify the flags of a register,

- implement C programs to control the input/output of the MipsIT I/O modules through polling.

#### Resources

We will use the same software as in previous sessions, i.e. the MipsIt programming environment.

## 2. Preliminary (pre-lab) work

For the pre-lab work for this session, all members of the workgroups should read the first two annexes to this document, which describe the MipsIt I/O space. You should also read Annex III, which describes C operators at bit level. These operators will prove very useful for this practice session. You should also review all the concepts of the computer I/O system you have studied so far in your theory classes.

After reading the annexes and the recommended bibliography, answer the following questions:

- 1. Briefly describe the data transfer synchronization method known as "polling".

- 2. Assume that we have a data entry module with a status register (which we call status), which has a value of 1 when there are data to be read and zero otherwise, and a data I/O register, from which we can read the data of the I/O module. Write a procedure, in pseudo-algorithmic language, that can read the data from that module and write them to a data variable.

- 3. What sources share the external interrupt line 3 in the MipsIt simulator?

- 4. What register should we read to check the status of buttons K1 and K2 and the external Timer signal associated with the MipsIt interrupt module (module 2 in the Annex)?

- 5. Describe how, by reading the state of the interrupt module (module 2 in Annex 2), we can determine whether at a given moment button K2 is being pressed.

- 6. Describe how, by reading the interrupt module status, we can determine whether the K2 button has been pressed. Explain what we should to avoid future false detections.

- 7. Suggest a sentence or a short C code fragment to detect whether K2 is being pressed. If it is, the value TRUE must be assigned to a Boolean variable.

- 8. Design a program to implement a shift of 1 LED along the bank of LEDs in module 1 (pseudocode or flowchart). First, the program must wait until the K1 button in module 2 has been pressed. Then, led0 will turn on and then go to led1 and so on until it reaches led7. At this point, the LED will go backwards by doing the reverse movement until it reaches led0 (Knight Rider style) and then it will start again. The program will end only in the led0 position if the K2 button has been pressed at any time. The timer must be used to control the LEDs' lighting time.

**First checkpoint:** Answers to Q1-Q8 must be written up and handed in to the lecturer at the beginning of the session.

## 3. Lab (in-lab) work

In this session we will see the programming and management of the I/O modules in a practical way. To do so, we will design several programs that involve the use of these modules.

**Second checkpoint**: Implement the counter program proposed in question 8 of the pre-lab tasks. Show the proper functioning of the program and code to your lecturer.

Bear in mind that the compiler's default options must be edited as in section 3.1 in P1 since we are accessing the processor's I/O space.

- 3.1 We propose implementing a C program in the MipsIt simulation environment to control a traffic light system. Assume that the traffic light system is made up of:

- 3 colours for the vehicle traffic lights: red, yellow and green

- 3 colours for the pedestrian traffic lights: red, yellow and green

To simulate the switching on and off of the lights, we will use the LEDs in I/O module 1. We divide them into 2 banks of 4 LEDs and assume that the red lamps are the 2 most significant LEDs in each bank. The yellow and green lamps must form the rest of the LEDs, in the same order.

The traffic light system must behave as follows:

- Initially the traffic light system always gives way to vehicles, so the lights must be green for cars and red for pedestrians.

- When a pedestrian presses the pedestrian crossing button (button K1 in module 2), the traffic light changes automatically, turning the traffic light for vehicles to yellow.

- After a certain wait period, the light must change again (this time to red) and the vehicle pass light plus the pedestrian traffic light must both change to green.

- When the pedestrian crossing time has finished, the pedestrian traffic light must turn to yellow, while the vehicle traffic light remains on red. The system must then return to its initial state.

To set the time in each state, the external timer (located in module 2) must be used. The time in each case must be:

- The yellow light must be *On* for 5 pulses of the external timer for both vehicles and pedestrians.

- The red light for vehicles (green for pedestrians) must be *On* for 20 pulses of the external timer.

Bear in mind that the compiler's default options must be edited as in section 3.1 in P1 since we are accessing the processor's I/O space.

**Third checkpoint**: The traffic light program must be implemented using the polling synchronization method and simulated within the MipsIt program. Show the proper functioning of the program and the code to your lecturer.

# Annex I: MipsIt I/O memory space

## Introduction

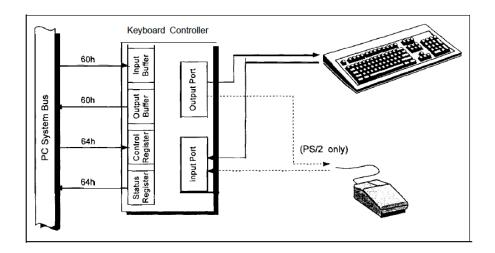

The input/output (I/O) system of a computer consists of the elements (buses, registers, protocols, etc.) that enable us to connect the computer to the peripheral devices.

An I/O operation can be divided into three phases:

- 1. **Addressing**: Access to the module through its memory address.

- 2. **Synchronization and control of the transfer**: The mechanism used to determine whether the peripheral is ready to begin a transfer (to send or to receive) data, control the transfer, and control whether another transfer can be started.

- 3. **Data transfer**: Transfer of the data itself, which may require transforming data sent by the peripherals.

Synchronization is a critical stage in I/O operations and fundamental for correct data transfer. It also has great influence on the final performance of the system. Three commonly used techniques exist: polling (software-driven I/O), interrupts, and direct memory transfer (DMA).

## Software-driven or interrupt-based synchronization

In the data transfer between the computer and the Input/Output (I/O) module, the CPU is responsible for transferring the memory data and sending them to the I/O module (in a write), or similarly, for storing the data from the I/O module in the memory (in a read).

The arrival of data from outside the computer is normally unpredictable and the program cannot know exactly when an I/O module will have available data that must be read. A method is therefore needed to synchronize the execution of the program in the CPU with the I/O modules. Through this synchronization, the I/O module notifies the CPU when data are waiting to be read or when the queue of the data to be written is empty.

## Polling (Software-driven) synchronization

With this method the CPU executes a program that directly controls the I/O transfer. The program is responsible for sending the order and waits until the data transfer is complete. The program continuously checks the I/O module status until the transfer is complete. The polling is commonly implemented via a loop that does not end until all the data are transferred.

### Interrupt-based synchronization

Through an interrupt request performed by the interrupt module, the I/O module notifies the CPU that there are data to transfer. However, the CPU is responsible for extracting the data from the module (in the case of reading) or for sending the data to the module (in case of writing). As in the previous case, therefore, each of the transferred data passes through the CPU.

# Annex II: MipSit Input/Output address space

## Elements in 0xBF900000 (Module 1)

This is an 8-bit input/output module consisting of 8 buttons (inputs) and 8 LEDs (outputs). The value of the push buttons can be read when position 0xBF900000 is accessed and the output value of the LEDs can be modified also by writing on this position. These elements cannot produce interrupts. In other words, when an input value is modified in the pushbuttons, no interrupt request is produced since this module has no associated interrupt line.

## Elements in 0xBFA00000 (Module 2)

Remember that in the 0xBFA00000 memory position there is an I/O module with the following elements connected:

- 1. Push button K2

- 2. Push button K1

- 3. Timer

These entries can be modified through the following window:

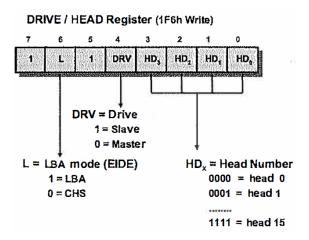

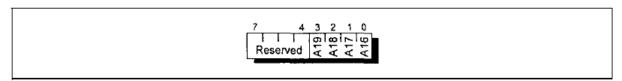

The status of each entry can be checked by reading 8 bits from the 0xBFA00000 position. Each bit has the following meaning:

- 0xBFA00000 Interrupts I/O (8-bit)

Bit:

- 0 – K2 (Input)

-1 - K1 (Input)

- 2 – Timer (Input)

- 3 - N/A (not defined)

- 4 − K2 latch

5 – K1 latch

- 6 – Timer latch

## - 7 – N/A (not defined)

When a button is pressed or the external timer is activated, an interrupt request is made. This request is associated with external interrupt line 3 connected to the microprocessor. The event that caused the interrupt remains stored in the corresponding latch. The value of the latch is not deactivated until a specific write is made on the same position 0xBFA00000, setting the bit to zero.

The three interrupt sources share the same microprocessor external interrupt line (line 3 of the IP6-2 interrupt lines). All three therefore produce the same hardware interrupt, which may or may not be enabled. To enable this interrupt through the interrupt mask of the Status register, we must set the 13th bit to 1, which corresponds to interrupt line IP5. Otherwise, the interrupt does not occur even though the bits of the status register of the 0xBFA00000 position are activated.

## Annex III: bitwise operations in C

## Introduction

The case we are interested in may operate data at bit level, e.g. to activate or deactivate specific flags. A flag is a bit-wide variable that can take two values. However, these flags are usually grouped in an integer or char variable ('short int', 'int', 'Unsigned char') since in C (and in most programming languages) there are no predefined bit types.

## **Bitwise operators**

To access these flags, or simply to activate or deactivate them, bitwise operators must be used. Though not very common, they are used when reading and writing in the I/O module registers and therefore when designing the programs that control them.

Below are the most common operators.

| Bit level | operators |

|-----------|-----------|

|-----------|-----------|

| Operator | Effect         |  |

|----------|----------------|--|

| &        | Bit level AND. |  |

|          | Bit level OR.  |  |

| ٨        | Bit level XOR. |  |

| ~        | Complement.    |  |

| <<       | Left shift.    |  |

| >>       | Right shift.   |  |

Bitwise operators work with variables of type char, short (2 bytes), int (4 bytes) and long (8 bytes) but not with float or double variables. Below we briefly describe each of these operators.