### DOCTORAT EN FÍSICA

Departament de Física Atòmica, Molecular i Nuclear Institut de Física Corpuscular (CSIC-UV)

# Contribuciones a la electrónica de adquisición y sincronismo del telescopio de neutrinos ${\rm KM3NeT}$

David Calvo Díaz-Aldagalán

DIRECTORES:

Juan Zúñiga Román Juan de Dios Zornoza Gómez

Valencia, marzo de 2021

## David Calvo Díaz-Aldagalán

Contribuciones a la electrónica de adquisición y sincronismo del experimento KM3NeT

Supervisores: Dr. Juan de Dios Zornoza Gómez y Dr. Juan Zúñiga Román

Valencia, marzo, 2021

#### Universidad de Valencia

${\bf Astroparticle\ Physics\ Group}$

Instituto de Física Corpuscular (CSIC-UV)

Dr. Juan de Dios Zornoza Gómez, Profesor Contratado Doctor del

departamento de Física Atómica, Molecular y Nuclear de la Facultad de

Física de la Universidad de Valencia.

Dr. Juan Zúñiga Román, Catedrático de la Universidad de Valencia en

el departamento de Física Atómica, Molecular y Nuclear de la Facultad

de Física.

CERTIFICAN:

Que la presente memoria, titulada "Contribuciones a la electrónica de

adquisición y sincronismo del telescopio de neutrinos KM3NeT", ha sido

realizada bajo su dirección en el Instituto de Física Corpuscular (centro

mixto Universidad de Valencia - CSIC) por D. David Calvo Díaz-

Aldagalán y constituye su tesis doctoral para optar al título de Doctor

por la Universitat de València una vez cursados los estudios en el

Doctorado en Física.

Y para que así conste, firman la presente en Valencia, a 28 de marzo de

2021.

Fdo.: Dr. Juan de Dios Zornoza Gómez

Fdo.: Juan Zúñiga Román

### **AGRADECIMIENTOS**

Desarrollar una tesis doctoral puede que sea uno de los logros académicos más duros y difíciles de conseguir. Para alcanzarlo no solo se debe tener la disposición de poder realizarla sino también estar rodeado de las personas adecuadas. Y este, por fortuna, ha sido mi caso.

Quisiera agradecer a mis tutores, Juan y Juande, su ayuda y su disposición. Mi agradecimiento no es solo con esta tesis, donde han sido magníficos, sino durante todos estos años en el IFIC, por cómo me acogieron desde el principio, por cómo me valoran, por lo bien que nos lo hemos pasado en los viajes de la colaboración, por tantas cosas...

Por supuesto a Juanjo. Gracias por tener siempre la puerta abierta para mí, y gracias por esas primeras conversaciones que tuvimos y que me hicieron apostar por continuar en el IFIC.

A mis Raners: Diego, Fernando y Alberto, por todo lo que me aportáis dentro y fuera de los laboratorios. Sois una de las razones principales por las que me encanta trabajar en el IFIC.

A mis amigos Javi Navarro, Javi Collado, Gess, Brambo y Ramón. Por todos esos momentos (y noches) que hemos compartido.

Gracias a César Domingo por toda tu ayuda y por todo tu apoyo desde que nos conocemos. Es un placer trabajar contigo. Eres uno de los físicos más ingenieriles que he conocido.

A mi amigo Alfonso, muchas gracias por tu apoyo desde siempre, por estar ahí desde hace tantos años y sobre todo durante la escritura de esta tesis.

To my Dutch friend Peter, thanks for all the virtual coffees and the technical discussions we have had during all these years. I have learned a lot from you.

Aunque no los tenga tan cerca, el gran apoyo de mi familia en todo lo que hago ha sido fundamental. Gracias a mis padres por su apoyo incondicional, por sus ánimos, y por todo lo que me aportan aun estando, desgraciadamente, tan lejos. Soy lo que soy gracias a vosotros y esta tesis también es el fruto de vuestro trabajo. Por supuesto, gracias a mi yaya, a mis tíos, primos, y a mi familia de Valencia, aunque este año no nos hayamos podido juntar, recuperaremos el tiempo perdido.

Mención especial para Carmen, mi pequeña. Gracias por todos los momentos que hemos vivido y por todos los que nos quedan por vivir, en especial a partir de ahora. No hay mejor persona con la que compartir la vida que tú. Te quiero.

# ÍNDICE

| 1 | INTR      | ODUCCIÓN                                           | 25 |

|---|-----------|----------------------------------------------------|----|

|   | 1.1       | Astronomía con neutrinos de alta energía           | 27 |

|   | 1.1.1     | Rayos cósmicos                                     | 28 |

|   |           | Γelescopios de neutrinos. Descripción y principios |    |

|   | detección | n                                                  | 31 |

|   | 1.2.1     | Fondo físico                                       | 33 |

|   | 1.2.2     | Fondo óptico                                       | 34 |

|   | 1.3       | Γelescopio de neutrinos ANTARES                    | 35 |

|   | 1.3.1     | Módulo óptico de ANTARES                           | 37 |

|   | 1.4       | Γelescopio de neutrinos KM3NeT                     | 38 |

|   | 1.4.1     | Módulo óptico de KM3NeT                            | 43 |

| 2 | ELEC      | CTRÓNICA DE ADQUISICIÓN                            | 47 |

|   | 2.1       | Central Logic Board                                | 48 |

|   | 2.2       | Power Board                                        | 49 |

|   | 2.3 I     | Bases de los fotomultiplicadores                   | 52 |

|   | 2.4       | Signal Collector Board                             | 54 |

|   | 2.5       | Nanobeacon                                         | 55 |

| 3 | CENT      | TRAL LOGIC BOARD                                   | 59 |

|   | 3.1 I     | Especificaciones de la tarjeta CLB                 | 60 |

|   | 3.2       | Componentes principales de la CLB                  | 61 |

|   | 3.2.1     | Field Programmable Gate Array                      | 61 |

|   | 3.2.2     | Transceptor óptico                                 | 63 |

|   | 3.2.3     | Sistema de reloj                                   | 65 |

|   |           | Sansoras de instrumentación                        |    |

|   | 3.2.5                                                                          | Configuración de la CLB                                   | .68                                                  |

|---|--------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|

|   | 3.2.6                                                                          | Interfaz serie USB                                        | .70                                                  |

|   | 3.2.7                                                                          | Sistema de reinicio                                       | .71                                                  |

|   | 3.3 I                                                                          | Diseño físico de la tarjeta                               | .72                                                  |

|   | 3.4                                                                            | Simulaciones previas al diseño                            | .76                                                  |

|   | 3.4.1                                                                          | Diseño de vías y análisis de sus efectos en la integridad | de                                                   |

|   | las sei                                                                        | ñales                                                     | .78                                                  |

|   | 3.5                                                                            | Simulaciones posteriores al diseño                        | .82                                                  |

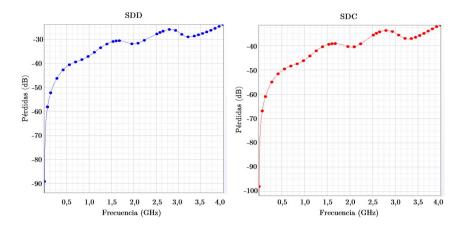

|   | 3.5.1                                                                          | Análisis de pérdidas y acoplo                             | .82                                                  |

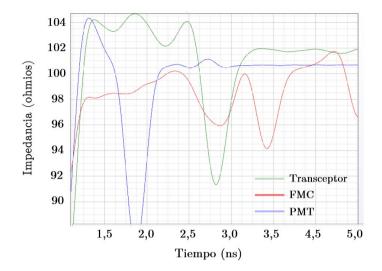

|   | 3.5.2                                                                          | Análisis de las fluctuaciones                             | .89                                                  |

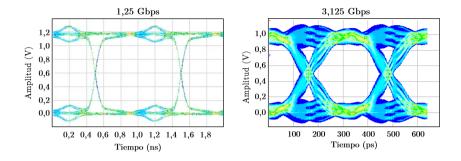

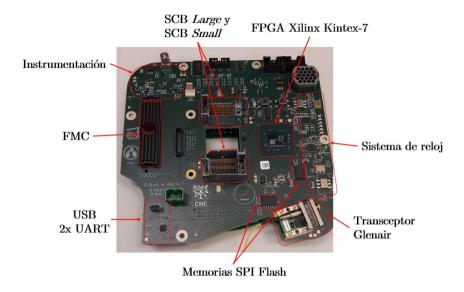

|   | 3.6 I                                                                          | Prototipo de la CLB                                       | .91                                                  |

|   | 3.6.1                                                                          | Análisis de los osciladores                               | .91                                                  |

| 4 | SINC                                                                           | RONISMO EN KM3NeT                                         | .97                                                  |

| • |                                                                                |                                                           |                                                      |

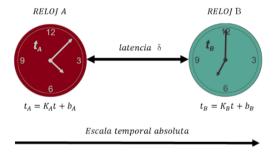

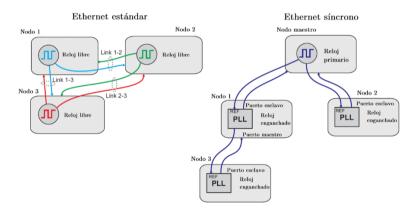

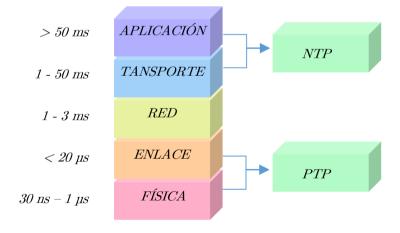

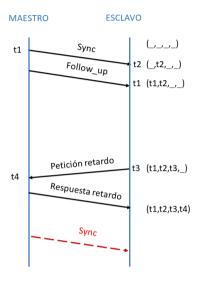

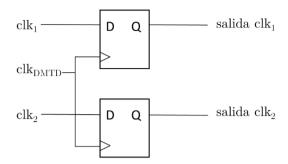

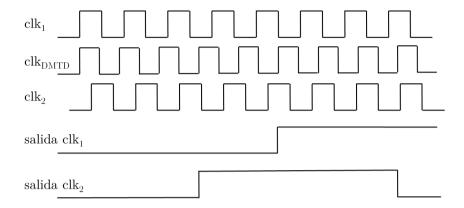

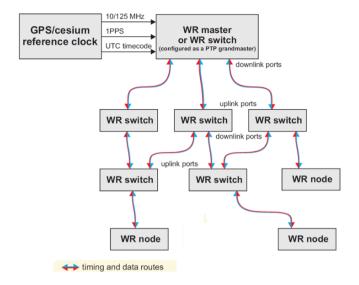

|   |                                                                                | Principios de sincronismo                                 | .98                                                  |

| • | 4.1 I                                                                          |                                                           |                                                      |

| • | 4.1 I                                                                          | Principios de sincronismo                                 | 104                                                  |

|   | 4.1 I<br>4.2 S<br>4.2.1                                                        | Principios de sincronismo                                 | 104<br>105                                           |

|   | 4.1 I<br>4.2 S<br>4.2.1<br>4.2                                                 | Principios de sincronismo                                 | 104<br>105<br>106                                    |

|   | 4.1 I<br>4.2 §<br>4.2.1<br>4.2.4                                               | Principios de sincronismo                                 | 104<br>105<br>106<br>108                             |

|   | 4.1 I<br>4.2 §<br>4.2.1<br>4.2.<br>4.2.<br>4.2.                                | Principios de sincronismo                                 | 104<br>105<br>106<br>108                             |

|   | 4.1 I<br>4.2 S<br>4.2.1<br>4.2<br>4.2<br>4.2<br>4.2.2                          | Principios de sincronismo                                 | 104<br>105<br>106<br>108<br>108<br>109               |

|   | 4.1 I<br>4.2 S<br>4.2.1<br>4.2<br>4.2<br>4.2<br>4.2.2                          | Principios de sincronismo  Sincronismo en KM3NeT          | 104<br>105<br>106<br>108<br>108<br>109<br>red        |

|   | 4.1 I<br>4.2 S<br>4.2.1<br>4.2<br>4.2<br>4.2<br>4.2<br>White                   | Principios de sincronismo  Sincronismo en KM3NeT          | 104<br>105<br>106<br>108<br>108<br>109<br>red<br>110 |

|   | 4.1 I<br>4.2 S<br>4.2.1<br>4.2<br>4.2<br>4.2<br>4.2<br>White<br>4.2.3<br>4.2.4 | Principios de sincronismo  Sincronismo en KM3NeT          | 104<br>105<br>106<br>108<br>109<br>red<br>110<br>113 |

|   | 4.2.5  | Red White Rabbit Híbrida para Fase 1                     |

|---|--------|----------------------------------------------------------|

| 5 | FIAB   | ILIDAD127                                                |

|   | 5.1 I  | Principios estadísticos                                  |

|   | 5.2    | Cálculo de las tasas de fallos                           |

|   | 5.2.1  | Factores físicos y tecnológicos                          |

|   | 5.2.2  | Factor de fabricación                                    |

|   | 5.2.3  | Factor de proceso                                        |

|   | 5.2.4  | Factor LF                                                |

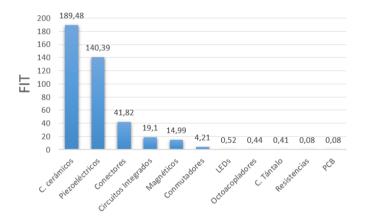

|   | 5.2.5  | Cálculo unitario de FIT para condensadores cerámicos 142 |

|   | 5.3 I  | Fiabilidad en el DOM                                     |

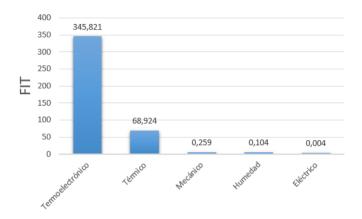

|   | 5.4 I  | Fiabilidad en el WRS                                     |

| 6 | FIRM   | WARE DE ADQUISICIÓN153                                   |

|   | 6.1 I  | Requisitos de adquisición                                |

|   | 6.2    | Time to Digital Converters156                            |

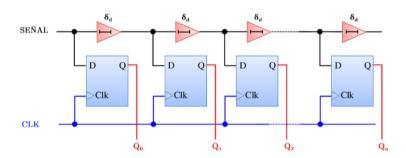

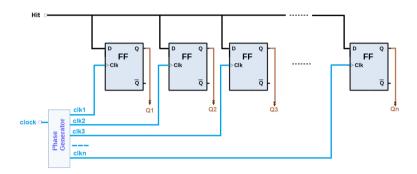

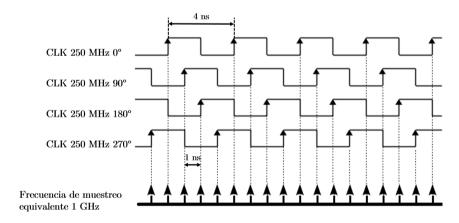

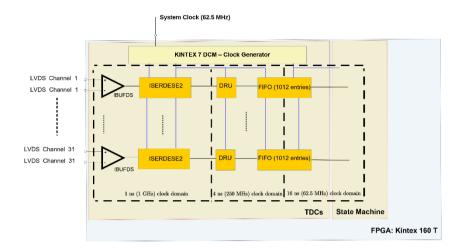

|   | 6.2.1  | Arquitectura de los Time to Digital Converters 157       |

|   | 6.2.2  | Características temporales                               |

|   | 6.2.3  | Implementación del sistema de adquisición basado en Timo |

|   | to Dig | gital Converters                                         |

|   | 6.2.4  | Funciones adicionales: Veto y Multihit                   |

|   | 6.2    | 4.1 <i>Multihit</i>                                      |

|   | 6.2    | 4.2 Veto                                                 |

|   | 6.2    | 4.3 Recursos utilizados                                  |

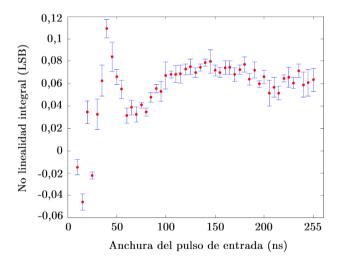

|   | 6.2.5  | Resolución y precisión                                   |

|   | 6.2.6  | No linealidad                                            |

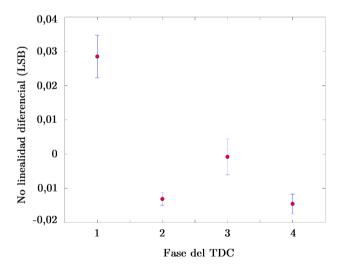

|   | 6.2    | .6.1 No linealidad diferencial                           |

| 10 | BIBLIOGRAFÍA                                           | 197 |

|----|--------------------------------------------------------|-----|

| 9  | LISTA DE ACRÓNIMOS                                     | 191 |

| 8  | LISTA DE PUBLICACIONES                                 | 189 |

| 7  | CONCLUSIONES                                           | 185 |

|    | 6.4 Resultados experimentales                          | 178 |

|    | 6.3.1 Arquitectura e implementación                    | 175 |

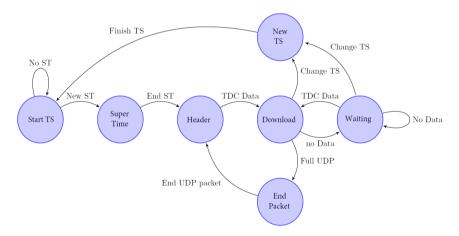

|    | 6.3 Procesado de datos                                 | 173 |

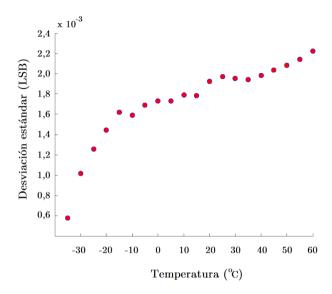

|    | 6.2.7 Caracterización de los efectos de la temperatura | 172 |

|    | 6.2.6.2 No linealidad integral                         | 171 |

### **PREFACIO**

Casi todo el conocimiento que se tiene sobre el Universo se ha obtenido mediante observaciones de ondas electromagnéticas, donde se engloban ondas de radio, infrarrojos, luz visible, luz ultravioleta, rayos X y rayos gamma. Sin embargo, además de los fotones, existen otros mensajeros cósmicos como los rayos cósmicos, los neutrinos o las recientemente descubiertas ondas gravitacionales, que pueden proporcionarnos conocimientos importantes para aumentar nuestra comprensión del Universo.

Los rayos cósmicos bombardean nuestra atmósfera continuamente desde el espacio con energías de hasta  $10^{20}$  eV. A pesar de que se han conseguido grandes avances para medir y entender su espectro de energía, han transcurrido más de 100 años desde su descubrimiento sin que se conozca con certeza su origen ni los mecanismos que consiguen acelerarlos a energías tan altas.

No obstante, en la generación y aceleración de los rayos cósmicos se producen rayos gamma y neutrinos, los cuales, por su naturaleza, pueden tener un papel fundamental para revelar el origen y el mecanismo de aceleración de estas partículas.

El neutrino tiene unas propiedades especiales que lo convierten en un mensajero cósmico único. Se trata de una partícula neutra, con apenas masa y que solo interacciona con la materia a través de la interacción débil. Esto le permite viajar enormes distancias sin que su trayectoria se vea alterada, así como atravesar objetos compactos y muy densos como el interior de las estrellas. Pero esas mismas propiedades hacen que su detección sea extremadamente difícil. Es por ello por lo que los detectores de neutrinos tienen que abarcar un volumen del orden de un km³ para poder detectarlos. Además, el principio de operación de los telescopios de neutrinos basado en la detección de fotones Cherenkov

hace necesario que estén ubicados dentro de un medio transparente de grandes dimensiones como puede ser el agua del fondo de los océanos, lagos profundos o el hielo antártico.

Los trabajos desarrollados en esta tesis doctoral se engloban dentro de la electrónica para la construcción de la infraestructura KM3NeT, una red de telescopios submarinos que estará ubicada en el fondo del mar Mediterráneo, y que una vez terminada, será el mayor telescopio de neutrinos construido hasta la fecha.

En la primera parte de esta tesis, en los capítulos 1 y 2, se presenta una introducción a KM3NeT, en particular a los estudios de física que pretende realizar y a la electrónica de sus módulos ópticos respectivamente.

El capítulo 3 está dedicado por completo a la tarjeta electrónica principal del experimento KM3NeT, la denominada *Central Logic Board*. En este capítulo se describen tanto el diseño como las funciones principales que dicha tarjeta desempeña.

El capítulo 4 contiene las contribuciones aportadas a la implementación de la red de sincronismo de KM3NeT. El difícil emplazamiento del experimento, así como su topología, hacen que sea necesario utilizar un robusto protocolo de sincronismo que permita obtener la resolución angular deseada.

También, en relación a la dificultad del emplazamiento del experimento, y la imposibilidad de realizar reparaciones en los módulos ópticos, la fiabilidad se convierte en un punto fundamental para garantizar la viabilidad de KM3NeT a largo plazo. Por ello, en el capítulo 5 se muestran de forma detallada los estudios de fiabilidad realizados a las principales tarjetas electrónicas que componen los módulos ópticos.

El capítulo 6 está enteramente enfocado al *firmware* desarrollado para el sistema de adquisición. En este capítulo se muestran con detalle todos

los componentes del sistema de adquisición, su verificación experimental en el laboratorio, así como los resultados obtenidos *in situ* con las primeras líneas instaladas en el fondo del mar que confirman dicha verificación.

Finalmente, en el capítulo 7 se exponen las conclusiones obtenidas con la realización de esta tesis doctoral.

# **INTRODUCCIÓN**

# 1 INTRODUCCIÓN

Hasta el siglo XX toda la astronomía y la información que se tenía de los astros provenía de la radiación electromagnética, donde se engloban las ondas de radio, infrarrojo, luz visible, luz ultravioleta, rayos X y rayos gamma. Todas estas formas de radiación tienen la misma naturaleza física. Sin embargo, existen otras partículas que también pueden actuar como mensajeros cósmicos ofreciendo una nueva forma de hacer astronomía y aportando otra visión del Universo. Entre estas partículas se encuentra el neutrino.

El neutrino es una partícula fundamental, fermiónica, neutra y de spin ½ dentro del Modelo Estándar de la física de partículas [1]. Se trata de una partícula con muy poca masa que, al contrario que los leptones con carga (electrón, muon y tau) y los quarks, únicamente interacciona con la fuerza débil y la fuerza gravitatoria. Esto los convierte en unas partículas ideales para la astronomía, ya que pueden atravesar enormes distancias y grandes cantidades de materia sin interactuar ni ser afectados por la fuerza fuerte ni por campos electromagnéticos. Estas propiedades únicas para la astronomía hacen, por otro lado, que su detección sea extremadamente difícil. De hecho, se han producido muy pocas detecciones de neutrinos extraterrestres. Los primeros neutrinos detectados procedían de las reacciones nucleares internas del Sol, en la década de los 70 [2]. La primera detección de neutrinos provenientes de fuera del sistema solar data de 1987 y fueron producidos por la explosión de la supernova SN1987A en la Gran Nube de Magallanes [3]. Recientemente, la colaboración IceCube [4], cuyo detector se encuentra situado en el fondo del hielo de la Antártida, observó neutrinos extraterrestres correspondientes a un flujo de neutrinos de alta energía y de origen desconocido [5].

Esta singular partícula fue propuesta en 1930 por Wolfgang Pauli para tratar de explicar y compensar la aparente violación de la conservación de la energía en la desintegración  $\beta$  de los neutrones [6],

$$n \to p^+ + e^- + \bar{\nu}_e$$

. (1.1)

Esta hipotética partícula de reducida sección eficaz y sin masa era casi indetectable debido a su escasa interacción con la materia, pero en 1956 físicos Cowan y Reines demostraron experimentalmente su existencia. Su experimento consistió en llenar dos tanques de agua y cloruro de cadmio para detectar los antineutrinos producidos por el reactor nuclear de Savanah River (Carolina del Sur) [2]. Los antineutrinos emitidos por el reactor interaccionarían con los núcleos de hidrógeno de las moléculas de agua de los tanques produciendo un neutrón y un positrón. El positrón se aniquilaría con un electrón dando lugar a dos fotones gamma que serían capturados y detectados en coincidencia por detectores de centelleo. Por su parte, el neutrón es absorbido por el cadmio, el cual se desintegrará produciendo un rayo gamma que también sería detectado por los fotomultiplicadores con un cierto retraso respecto a los fotones procedentes de la aniquilación  $e^+$   $e^-$ . Tras varios meses de toma de datos, se confirmó la existencia del neutrino, con una tasa de detección de tres neutrinos por hora [7].

Los experimentos sobre neutrinos continuaron y la primera evidencia de la existencia de diferentes tipos (o sabores) de neutrinos se obtuvo en 1962 con el experimento Brookhaven [8] donde los antineutrinos producidos por la desintegración de los piones colisionaban con los protones produciendo antimuones. Existen tres tipos de neutrinos: electrónico ( $\nu_e$ ), muónico ( $\nu_\mu$ ) y tau ( $\nu_\tau$ ) aunque el neutrino tau no fue observado hasta el año 2000 por la colaboración DONuT [9].

## 1.1 Astronomía con neutrinos de alta energía

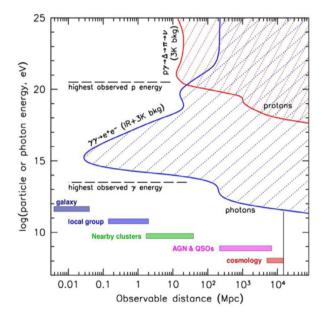

El uso de neutrinos en la astronomía como partículas mensajeras tiene varias ventajas respecto a la astronomía con fotones o protones. Debido a las interacciones con la luz infrarroja o con el fondo cósmico de microondas (*Cosmic Microwave Background* - CMB), la máxima distancia del Universo que puede observarse con rayos gamma de energías superiores a  $10^{12}$  eV está entre 0,03 Mpc y 200 Mpc. En el caso de los protones de alta energía (mayores de  $10^{20}$  eV) el máximo Universo observable es de 30 Mpc, como se ilustra en la figura 1.1. Estas limitaciones no afectan a la astronomía con neutrinos ya que solo interaccionan con la fuerza gravitatoria y con la fuerza nuclear débil, por lo que el Universo se puede considerar trasparente para ellos [10].

Figura 1.1. Universo observable en función de la energía de los fotones (azul) y en función de la energía de los protones (línea roja). Las zonas con trazo discontinuo indican la zona del Universo no observable. Imagen obtenida de [11].

#### 1.1.1 Rayos cósmicos

Los rayos cósmicos son partículas y núcleos cargados estables que, procedentes del espacio exterior, bombardean continuamente la Tierra. El descubrimiento de este fenómeno fue realizado en 1912 por Victor Hess, quien observó que el flujo de estas partículas aumentaba a medida que ascendía en un globo aerostático [12]. Por lo tanto, pudo confirmar su origen extraterrestre y descartar un origen procedente del interior de la Tierra. Actualmente se sabe que, hasta unos pocos TeV, los rayos cósmicos son núcleos ligeros, protones (89%), helio (10%) y núcleos más pesados (1%).

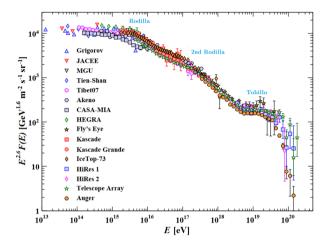

El origen de los rayos cósmicos ha presentado incógnitas desde su descubrimiento hace más de 100 años. El espectro de energía de los rayos cósmicos que llegan a la Tierra es muy amplio, mostrando incluso partículas con energía superior a  $10^{20}$  eV. Estas energías sugieren la existencia de aceleradores hadrónicos en el espacio, aunque aún no se ha encontrado evidencia de tales aceleradores. El espectro de energía de los rayos cósmicos se puede describir mediante una ley de potencias,

$$\frac{dN}{dE} \propto E^{-\alpha},$$

(1.2)

donde E representa la energía de la partícula primaria y  $\alpha$  se denomina índice espectral. A los rayos cósmicos por debajo de unos pocos GeV se les supone origen solar o que están afectados por el campo magnético solar. Para energías superiores, dependiendo del valor del índice espectral, se pueden distinguir tres zonas dentro del rango de energía que pueden estar relacionadas con el origen y mecanismo de producción de los rayos cósmicos.

➤ La primera zona, con un índice espectral de 2,7 comprende los rayos cósmicos entre pocos GeV y 400 TeV (punto denominado "rodilla"). Se supone que se originan y se aceleran en primera

- instancia por remanentes de Supernova (Supernova remmants SNRs) y posteriormente por campos magnéticos galácticos.

- ➤ La siguiente zona, cuyo índice espectral es 3,3, comprende rayos cósmicos entre los 400 TeV y los 3 EeV (punto denominado "tobillo"). A estos rayos cósmicos se les supone también un origen galáctico, aunque diferente al de la zona anterior. Para esta zona se han propuesto orígenes como púlsares, sistemas binarios u objetos masivos como agujeros negros, o estrellas de neutrones.

- ➤ La última zona corresponde a los denominados rayos cósmicos ultra energéticos (Ultra High Energy Cosmic Rays UHECRs). Se trata de rayos cósmicos de energía superior a la del punto "tobillo". En esta zona el índice espectral es 2,6 y se les supone un origen extragaláctico, como núcleos activos de galaxias (Active Galactic Nuclei AGNs) o estallidos de rayos gamma (Gamma-Ray Bursts GRBs).

La figura 1.2 muestra los resultados recogidos por varios experimentos donde se muestran estas tres zonas delimitadas por un cambio de pendiente asociado a la variación del índice espectral.

Para intentar comprender el origen de los rayos cósmicos y los mecanismos de aceleración sobre partículas de alta energía, se han realizado diversos estudios y observaciones mediante fotones con energías desde el infrarrojo hasta los rayos gamma. Los fotones no tienen carga eléctrica, por lo que pueden recorrer grandes distancias sin modificar su trayectoria. Esto permite reconstruir la dirección hacia su fuente de origen. Sin embargo, actualmente existe una cierta controversia sobre si los rayos gamma observados han sido producidos por electrones relativistas o por rayos cósmicos. En este sentido existen dos tipos de modelos que explicarían el origen de los rayos gamma. En los modelos leptónicos, los rayos gamma se producen por la interacción

de los electrones relativistas con los propios fotones sincrotrón que ellos mismos producen mediante la dispersión Compton inversa [13].

**Figura 1.2.** Espectro de energía de los rayos cósmicos detectados por diferentes experimentos. Se observa la variación de índice espectral. Imagen adaptada de [14].

En los modelos hadrónicos, son los protones acelerados los que al interaccionar con la radiación ambiental darían lugar no solo a rayos gamma, sino también a neutrinos de alta energía mediante la producción de piones a través de la resonancia  $\Delta$ ,

$$p + \gamma \rightarrow \Delta^+ \rightarrow \begin{cases} \pi^0 + p \\ \pi^{\pm} + n \end{cases}$$

(1.3)

De esta manera, los piones neutros se desintegran dando lugar a fotones mientras que los piones cargados lo hacen produciendo neutrinos,

$$\begin{array}{ll} \pi^0 \rightarrow & 2\gamma \\ \pi^+ \rightarrow & \nu_\mu + \mu^+ \cdot \\ \pi^- \rightarrow & \bar{\nu}_\mu + \mu^- \end{array} \eqno(1.4)$$

En este proceso los protones podrían quedar confinados dentro del campo magnético, mientras que los neutrones y neutrinos escaparían haciendo posible su detección. En este sentido, la observación de fuentes específicas de neutrinos sería clave para resolver el origen de los rayos cósmicos.

Por otra parte, los protones cuya trayectoria es desviada por campos magnéticos galácticos, si tienen una energía superior a  $10^{18}$  eV, serían levemente afectados por los campos magnéticos, por lo que podrían ser unos buenos candidatos para hacer astronomía con ellos e intentar buscar fuentes de UHECR. Por desgracia, a partir de 60 EeV, los rayos cósmicos pueden interaccionar con el CMB, también a través de la producción de la resonancia  $\Delta$ , perdiendo energía en forma de piones, lo que limitará su horizonte a decenas de Mpcs. Este efecto se conoce como el límite Greisen-Zatsepin-Kuzmin (GZK) [15, 16].

La motivación principal para hacer astrofísica de neutrinos de alta energía es el papel único y complementario que los neutrinos podrían desempeñar en nuestra observación de rayos cósmicos de alta energía. Los neutrinos se propagan a través del Universo casi sin sufrir perturbaciones a las energías más altas y sin desviarse en los campos magnéticos. Por lo tanto, se pueden utilizar como partículas mensajeras astronómicas para energías donde los rayos gamma o los protones no llegan, abriendo la posibilidad de una nueva ventana en el Universo de alta energía. Sin embargo, las estimaciones del flujo de neutrinos indican que sus detectores deben tener una escala mínima del orden del kilómetro cúbico para alcanzar la sensibilidad necesaria.

# 1.2 Telescopios de neutrinos. Descripción y principios de detección.

La capacidad que tienen los neutrinos para poder explorar algunos de los fenómenos más espectaculares del Universo choca con la dificultad de su detección, incluso a altas energías donde su sección eficaz es mayor.

En el proceso de desintegración beta inverso [17] utilizado por Ray Davis para estudiar los neutrinos solares, se utilizó un tanque con átomos de cloro (<sup>37</sup>Cl) que al absorber un neutrino electrónico decaería en un leptón, en este caso un electrón, y un átomo de argón (<sup>37</sup>Ar) por lo que, contando el número de átomos de argón, se obtendría el número de neutrinos. Este método no es muy adecuado para telescopios de neutrinos de alta energía ya que, además de ser un método muy tedioso, no proporciona información sobre la dirección del neutrino.

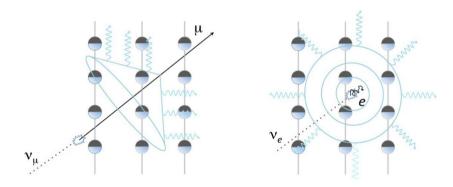

En cambio, en detectores como Super-Kamiokande la identificación se basa en la detección de la luz Cherenkov emitida por los leptones producidos en la interacción del neutrino con núcleos del detector. Esta radiación se emite cuando las partículas cargadas atraviesan un medio a velocidades relativistas, cuya velocidad de grupo es mayor que la velocidad de la luz en el medio. Las partículas cargadas polarizan los átomos del medio a su paso, los cuales cuando vuelven al equilibrio emiten fotones de Cherenkov en un frente de onda de luz coherente que puede reconstruirse utilizando tubos fotomultiplicadores (PhotoMultiplier Tubes - PMTs). Este frente de onda forma un cono con un ángulo respecto a la traza del leptón que viene dado por la expresión

$$\cos \theta = \frac{1}{\beta n},\tag{1.5}$$

donde  $\beta$  representa el cociente entre la velocidad de grupo del leptón y la velocidad de la luz en el vacío y n representa el índice de refracción del medio. Con estos datos, el ángulo del cono de radiación de Cherenkov está entre 43° - 45° para el agua y 40° para el hielo.

A energías suficientemente altas, el leptón secundario emergerá aproximadamente co-lineal con el neutrino entrante, lo que permitirá reconstruir la dirección de dicho neutrino. Esto es particularmente ventajoso en la detección de neutrinos muónicos, ya que los muones

secundarios producidos en una interacción de neutrinos pueden propagarse varios kilómetros a altas energías (> 100 GeV), lo que permite la detección de eventos físicos que se originen incluso fuera del volumen instrumentado. Los sucesos que producen este patrón en el detector se denominan sucesos tipos traza.

Existe otro tipo de interacción de neutrinos que da lugar a un patrón diferente. Las interacciones de neutrinos electrónicos y algunas interacciones de neutrinos tau generan las denominadas cascadas hadrónicas y electromagnéticas, caracterizadas por emisiones de luz de corta distancia y esféricamente simétricas. La figura 1.3 muestra una representación de los sucesos tipos traza y los sucesos cascada.

Figura 1.3. Ilustración de la interacción de un neutrino muónico y la detección del leptón secundario emitido mediante radiación de Cherenkov en un medio transparente, como agua o hielo, para un suceso de tipo traza (izquierda). Interacción de un neutrino electrónico y la generación del suceso denominado cascada (derecha). Imágenes obtenidas de [18].

#### 1.2.1 Fondo físico

La mayoría de los eventos físicos detectados en un telescopio de neutrinos son los denominados eventos de fondo. Se trata, principalmente, de muones y neutrinos producidos por la interacción de rayos cósmicos con los núcleos de la atmósfera terrestre.

Los telescopios de neutrinos se suelen situar en lugares de mucha profundidad para tratar de apantallar y reducir el fondo de muones atmosféricos. Estos eventos atmosféricos tienen una trayectoria descendente, por lo que una forma de rechazarlos consiste en eliminar aquellos que tengan dirección descendente en la reconstrucción. Sin embargo, los rayos cósmicos que interaccionan con la atmósfera del hemisferio sur, pueden generar neutrinos atmosféricos que pueden atravesar toda la Tierra e interaccionar en las inmediaciones del detector. Este hecho dificulta la detección de eventos que vengan de fuentes cósmicas.

Para discriminar el fondo producido por los neutrinos atmosféricos existen técnicas de detección y filtrado especiales. Los neutrinos atmosféricos están distribuidos isotrópicamente sobre el cielo terrestre, por lo que una fuente cósmica localizada en un punto del mapa celeste, produciría una acumulación de eventos capaz de sobresalir sobre el fondo de neutrinos atmosféricos. Otro aspecto que permite diferenciarlos es que los neutrinos cósmicos tienen un espectro de energía más pronunciado a altas energías que el espectro de neutrinos atmosféricos.

#### 1.2.2 Fondo óptico

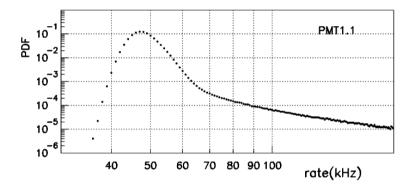

Finalmente, también hay un fondo adicional de fotones denominado fondo óptico cuyas principales fuentes son las desintegraciones radiactivas del isótopo <sup>40</sup>K, que abunda de manera natural en la sal del agua del mar, y la bioluminiscencia.

Los electrones producidos en las desintegraciones de <sup>40</sup>K tienen suficiente energía para generar luz Cherenkov. Dichas desintegraciones ocurren aleatoriamente en todas partes del volumen de detección y en la gran mayoría de los casos no están correlacionados en el espacio y el tiempo. Por tanto, la posibilidad de que la detección de varios fotones en coincidencia se confunda con un evento de neutrinos es bastante baja. Sin embargo, el fondo constante de los fotones del <sup>40</sup>K supone un

impacto en los requisitos del sistema de adquisición y filtrado que, como se verá en los siguientes capítulos, hay que tener en cuenta.

La otra fuente de fondo óptico la constituyen los organismos marinos luminiscentes, incluidos peces, crustáceos, moluscos, plancton, bacterias, etc. Se ha comprobado que la bioluminiscencia tiene dos componentes. Una emisión global que varía lentamente y se encuentra distribuida uniformemente en todo el detector, que se debe a organismos unicelulares que emiten de forma continua, (por ejemplo, bacterias) y las ráfagas de luz bioluminiscente, capaces de iluminar varios módulos ópticos agrupados localmente cuya duración puede ser de hasta varios segundos. Tales ráfagas pueden ser extremadamente brillantes pudiendo emitir hasta  $10^{13}$  fotones con el consiguiente impacto en el sistema de adquisición de datos.

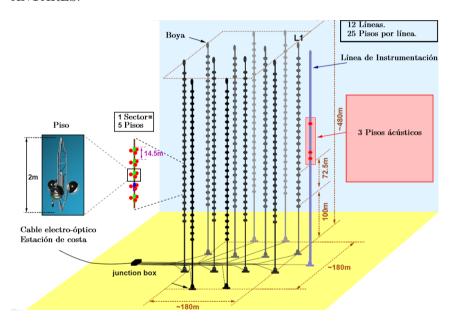

#### 1.3 Telescopio de neutrinos ANTARES

ANTARES (Astronomy with a Neutrino Telescope and Abyss environmental RESearch Project) [19] fue el primer telescopio de neutrinos operando en el mar y es, hasta la construcción de KM3NeT (Cubic Kilometre Neutrino Telescope), el más grande del hemisferio norte. El telescopio de neutrinos ANTARES está localizado a 40 km de la costa de Toulon (42° 48' N, 06° 10' E) a 2475 m de profundidad. Consta de 885 PMTs, repartidos en 12 líneas de detección, y una línea de instrumentación. Las líneas están formadas por 25 pisos cada una v tres módulos ópticos por piso. Cada módulo óptico contiene un PMT. Las líneas están ancladas al fondo del mar por una estructura de titanio y se mantienen verticales mediante un sistema de boyas. La separación media entre líneas es de 60-70 m mientras que la separación entre pisos es de 14,5 m. La primera línea del telescopio fue instalada en el año 2006 y su construcción finalizó en el año 2008. Desde entonces sigue funcionando y tomando datos ininterrumpidamente. La figura 1.4 muestra un esquema del detector ANTARES. Está previsto su desmantelamiento en 2021.

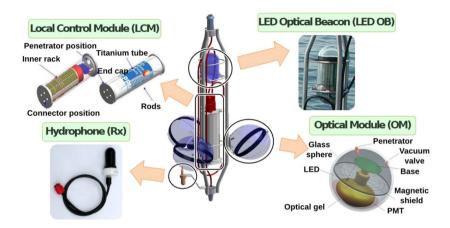

Los pisos consisten en estructuras de titanio que sujetan tres módulos ópticos los cuales están orientados a 45° hacía abajo respecto a la horizontal. Los pisos tienen en el centro el denominado *Local Control Module* (LCM), una estructura cilíndrica de titanio con la electrónica de control de los tres módulos. Cada cinco pisos hay un hidrófono para controlar el posicionamiento del detector. En los pisos 2, 9, 15 y 21 de cada línea se encuentran los denominados *LED optical Beacons*, un sistema basado en fuentes pulsadas tipo LED que permiten la calibración temporal del detector, así como monitorizar las propiedades ópticas del agua. La figura 1.5 muestra un esquema de los pisos de ANTARES.

Figura 1.4. Representación del telescopio de neutrinos ANTARES donde se aprecia la estructura en líneas de detección y la composición de los pisos. Imagen adaptada de [20].

**Figura 1.5.** Estructura y composición de los pisos que forman las líneas del detector ANTARES. Imagen obtenida de [10].

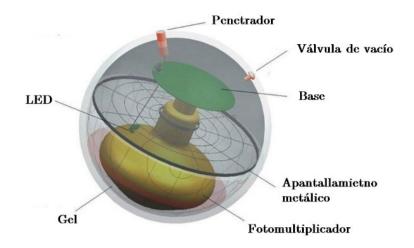

### 1.3.1 Módulo óptico de ANTARES

Los módulos ópticos de ANTARES, conocidos como Optical Modules (OMs), son esferas de vidrio de 43,1 cm de diámetro y un grosor de 15 mm capaces de soportar una presión de 260 atm. Incorporan un PMT de Hamamatsu modelo R7081-20 de 25,4 cm de diámetro. Estos PMTs tienen un Transit Time Spread (TTS) por debajo de 3 ns y una eficiencia cuántica del 25% para longitudes de onda de 400 nm. Para evitar que el campo magnético terrestre afecte al comportamiento de los PMTs, el módulo óptico contiene una red de mu-metal de alta permeabilidad magnética. Para garantizar una apropiada transmisión de los fotones y evitar desviaciones, el espacio entre el PMT y la esfera de vidrio se rellena con un gel óptico transparente con índice de refracción similar al del vidrio de la esfera. La parte trasera del OM está pintada de negro para evitar reflexiones de luz internas. La figura 1.6 muestra una imagen de los OM de ANTARES.

Figura 1.6. Módulo óptico utilizado en ANTARES. Figura modificada de [21].

## 1.4 Telescopio de neutrinos KM3NeT

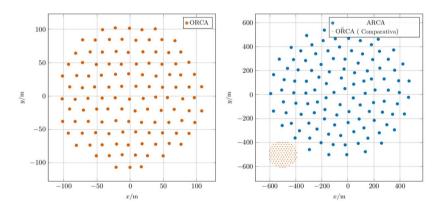

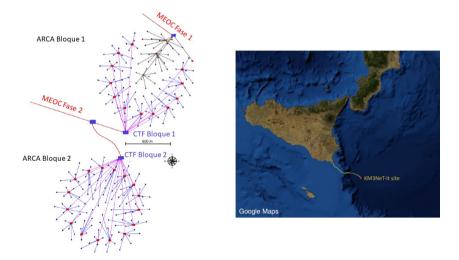

La colaboración KM3NeT [22] está construyendo una red de telescopios de neutrinos distribuidos por el mar Mediterráneo con dos objetivos principales: la detección de neutrinos de origen cósmico y la determinación del ordenamiento de masas de los neutrinos. Este detector estará formado por bloques, denominados Building Blocks (BBs), de 115 líneas llamadas Detection Units (DUs). Cada DU estará compuesta por 18 módulos ópticos, llamados Digital Optical Modules (DOMs). Los DOMs de las DUs se mantienen verticales y alineados mediante un sistema de boyas. La figura 1.4 muestra una representación de una DU junto con un DOM.

El telescopio KM3NeT, en su Fase 2, estará situado en dos zonas: la zona italiana, situada a unos 100 km de la costa de Capo Passsero, concretamente en las coordenadas 36° 16' N, 16° 06' E, donde se ubicará el detector ARCA (*Astroparticle Research with Cosmics in the Abyss*), que estará dedicado principalmente a la detección de neutrinos de origen cósmico, y la zona francesa, situada a unos 40 km de la costa de Toulon

(42° 48' N, 06° 02' E), donde se ubicará el detector ORCA (*Oscillation Research with Cosmics in the Abyss*), cuyo principal objetivo es determinar el ordenamiento de masas de los neutrinos.

Ambos detectores, ARCA y ORCA, comparten la misma tecnología, pero se diferencian en la distancia de separación entre los DOMs y entre las DUs, que está optimizada para abarcar el rango de energía de los neutrinos según el objetivo físico en cada detector. En ARCA, las DUs estarán separadas 95 m en promedio y los DOMs estarán separados 36 m en la dirección vertical, empezando a 80 m desde el fondo del mar, alcanzando una altura de 692 m. Cada BB de ARCA cubrirá un volumen de 0,48 km³. Los BBs de ARCA están diseñados para optimizar la detección de neutrinos de fuentes galácticas en un rango de energía entre unos pocos TeV y unos pocos PeV.

Figura 1.4. Representación parcial de una DU de KM3NeT (izquierda) junto con la imagen de un DOM (derecha). Imagen obtenida de [22].

En ORCA las DUs estarán separadas 20 m y los DOMs estarán separados 9 m en dirección vertical, empezando a 40 m desde el fondo del mar, alcanzando una altura de 193 m y cubriendo un volumen de

0,006 km<sup>3</sup>. Este bloque del experimento estará destinado a la detección de neutrinos de energías comprendidas entre los 3-100 GeV.

A modo de ejemplo, la figura 1.5 muestra una comparativa de los tamaños de un BB de ARCA y ORCA.

La construcción y producción de los componentes de ambos detectores está escalonada en fases. El objetivo de la denominada Fase 1 era instalar las primeras líneas, concretamente 6 DUs en ORCA y 24 DUs en ARCA. Estas líneas también formarán parte de la denominada Fase 2. Las 6 DUs de ORCA ya se encuentran instaladas y operativas. De ARCA hay 2 DUs instaladas. Para la primavera de 2021 se prevé instalar 5 DUs más, y el resto estarán instaladas en 2022.

**Figura 1.5.** Comparativa de tamaño entre los detectores de ARCA y ORCA del experimento KM3NeT.

Actualmente, el experimento se encuentra inmerso en la producción de la denominada Fase 2, la cual pretende terminar dos BBs de ARCA para el año 2025 y un BB de ORCA para el año 2024.

Los dos BB del experimento ARCA estarán situados a 3500 m de profundidad. Dos cables electro-ópticos, denominados MEOCs (*Main Electro-Optical Cables*) conectarán los 100 km de la estación de la costa con el detector. Un MEOC está compuesto por 20 fibras ópticas de tipo

G655 para transferencia de datos y un conductor eléctrico capaz de transportar 100 kW. Uno de los MEOC se conectará a ambos bloques mediante los denominados CTFs (Cable Termination Frames). En los CTFs hay un convertidor de voltaje, denominado Medium Voltage Converter (MVC), que transforma la tensión de 10 kV en corriente continua (Direct Current – DC) que transporta el MEOC en una tensión de 375 V DC [23]. Cada CTF se conectará con puntos de conexión denominados Junction Boxes (JBs). En la Fase 1, el CTF conectará 3 JBs en el bloque 1. En la Fase 2, los CTFs conectarán 16 JBs en el bloque 1 y 12 JBs en el bloque 2. Los JBs estarán separados entre ellos 95 m, siendo cada JB capaz de suministrar la alimentación y la conexión óptica a 12 DUs como máximo en la Fase 1 y a 7 DUs como máximo en la Fase 2. La figura 1.7 muestra un esquema de la finalización de la Fase 2 de ARCA y su localización física.

Figura 1.7. Esquema de la Fase de 2 de ARCA. Los puntos de color rojo representan las JBs mientras que los puntos azules representan las DUs (izquierda). Localización física de los dos bloques de ARCA en el mar Mediterráneo (derecha). Imagen adaptada de [22].

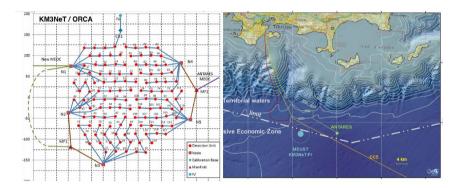

Por su parte, ORCA consistirá en un solo BB situado a 2450 m de profundidad. En este emplazamiento dos MEOCs conectarán la estación

de la costa con el detector. Los MEOCs de ORCA estarán compuestos de 36 y 48 fibras ópticas y un cable de alimentación. Las señales de los MEOCs se conectarán a cinco JBs. Cada JB tiene ocho conectores, donde cada conector es capaz de alimentar un máximo de 4 DUs. En ORCA, la alimentación se envía desde la estación de la costa en corriente alterna (*Alternating Current* – AC) a 3,7 kV AC y en la JB se transforma a 400 V AC. Posteriormente, en las bases de las DUs se transforma a 400 V DC. Las figuras 1.8 y 1.9 muestran una representación del BB de ORCA y una imagen de un JB, respectivamente.

Figura 1.8. En la figura de la izquierda se representa un esquema del plano de la Fase de 2 de ORCA. Los cuadrados de color marrón representan las cinco JBs mientras que los puntos rojos representan las DUs. A la derecha se muestra el emplazamiento del detector. Imagen obtenida de [22].

**Figura 1.9.** JB utilizado en ORCA (izquierda). Esquema de conexiones del JB con las DUs de ORCA (derecha). Imagen adaptada de [22].

### 1.4.1 Módulo óptico de KM3NeT

Los denominados Digital Optical Modules constituyen el elemento principal del detector KM3NeT. Los DOMs consisten en esferas de vidrio que contienen 31 PMTs junto con el sistema de alimentación, adquisición e instrumentación. Los modelos de PMT utilizados son ETEL D792KFL y Hamamatsu R12199-02. Tienen un TTS de 4,5 ns y su eficiencia cuántica es, aproximadamente, un 27% para longitudes de onda de 404 nm. Los PMTs están distribuidos sobre la superficie del DOM en cinco anillos de seis PMTs cada uno. Los PMTs están equidistantes dentro de un mismo anillo y los anillos están separados 30°. Se utiliza gel refractivo para rellenar el espacio que queda entre la esfera de vidrio y los PMTs.

El uso de varios PMTs dentro del DOM hace que el área efectiva de fotocátodo se incremente en un factor 3, permite detectar y distinguir más de un fotón llegando al mismo DOM y mejora la capacidad de discernir eventos de fondo generados por <sup>40</sup>K o bioluminiscencia. El hecho de ser más pequeños, comparados con los utilizados en ANTARES, hace que el campo magnético terrestre no les afecte, por lo que el DOM de KM3NeT no necesita de apantallamiento magnético.

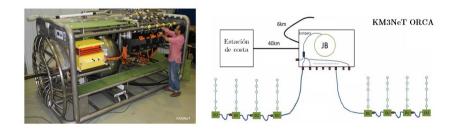

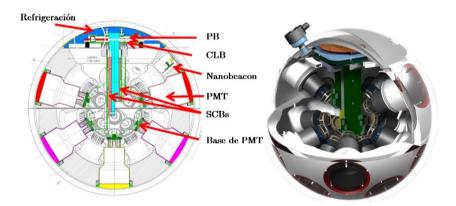

# 2 ELECTRÓNICA DE ADQUISICIÓN

Como se ha mencionado anteriormente, el DOM es el elemento principal en el que está basado el telescopio KM3NeT [24]. Además, tanto para ARCA como para ORCA se utiliza el mismo tipo de DOM. Toda la electrónica necesaria para controlar el funcionamiento de los DOMs se encuentra en su interior, rodeada por los 31 PMTs. La tarjeta electrónica principal se denomina Central Logic Board (CLB) y es la que gestiona y controla todas las funcionalidades del DOM. Conectada a la CLB se encuentra la Power Board (PB) cuya misión es generar todas las tensiones que necesita el DOM. Los PMTs están conectados a unas tarjetas denominadas bases, encargadas de generar la tensión de alimentación del PMT, así como de digitalizar su señal eléctrica para ser enviada a la CLB. Las denominadas Signal Collector Boards (SCBs) son las dos tarjetas que envían las señales de las bases de los PMTs a la CLB para su procesamiento. Por último, todos los DOMs llevan incorporado un dispositivo, denominado Nanobeacon, para la calibración temporal que utiliza un LED pulsado. La figura 2.1 muestra una imagen del DOM junto con todas las tarjetas electrónicas que lo componen.

**Figura 2.1.** Esquema del DOM con todas sus tarjetas electrónicas (izquierda) junto con su esquema 3D (derecha). Imagen adaptada de [25].

### 2.1 Central Logic Board

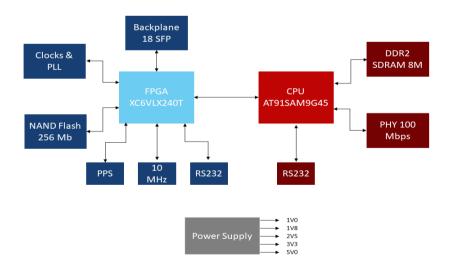

La denominada CLB es el elemento principal del sistema de adquisición de KM3NeT [26]. Se trata de una tarjeta electrónica multicapa que controla el funcionamiento del DOM, incluyendo la parte de adquisición, sincronismo, instrumentación y las diferentes interfaces de comunicación.

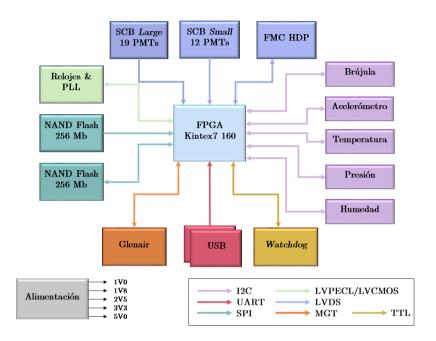

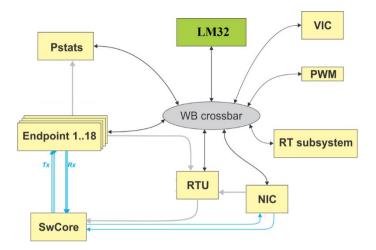

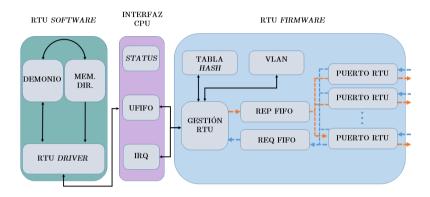

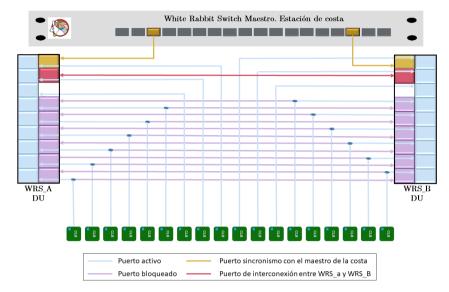

El control de todos los componentes de la tarjeta electrónica se ha implementado sobre una *Field-Programmable Gate Array* (FPGA) Kintex-7 de la compañía Xilinx Inc. La FPGA es la encargada de realizar la adquisición y digitalización de los eventos generados por los PMTs y de los eventos del sistema de posicionamiento acústico recogidos por un sensor piezoeléctrico.

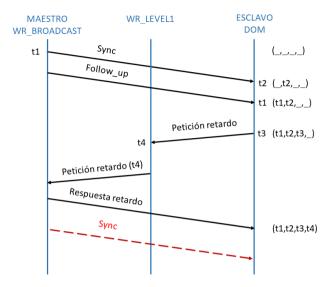

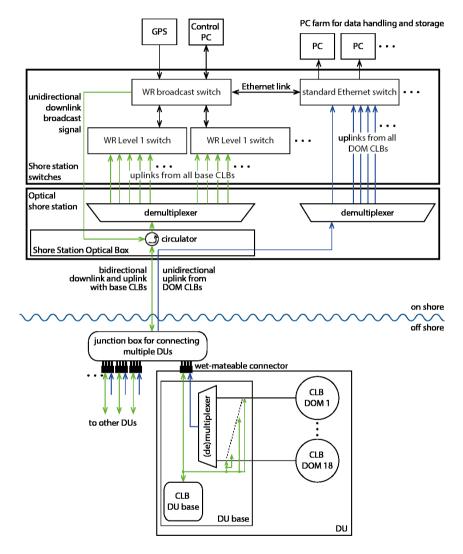

Todos los eventos, tanto ópticos como acústicos se digitalizan con una marca de tiempo proporcionada por el protocolo de sincronismo *White Rabbit* (WR), un protocolo que permite sincronizar todos los nodos de KM3NeT con una precisión de 1 ns. Dicho protocolo de sincronismo se describirá con detalle en el capítulo 4.

La FPGA tiene dos microprocesadores empotrados desarrollados por la compañía Lattice Semiconductor Corporation, uno de ellos para controlar el protocolo de sincronismo y el otro para gestionar el resto de funciones (adquisición, instrumentación, conexiones, comunicación y arranque). El sistema de adquisición de KM3NeT está basado en el modelo "all-data-to-shore", una estrategia donde todos los datos se envían a la estación de la costa sin filtrar. Allí, una granja de ordenadores se encarga de filtrar los datos y de reconstruir los eventos físicos. Para poder reconstruir dichos eventos físicos se ha establecido una jerarquía de niveles para las señales detectadas en los fotomultiplicadores denominada niveles de trigger:

- ➤ L0.- Es el nivel más básico y son las señales analógicas cuya amplitud es mayor que un determinado umbral predefinido, típicamente 0,3 pe (photoelectron).

- ➤ L1.- El nivel 1 de *trigger* se da cuando tiene lugar una coincidencia de al menos dos o más sucesos L0 en el mismo DOM en una ventana temporal (típicamente el valor de esta ventana es de 10 ns). La tasa de detección esperada por un DOM de eventos L1 es de 1 kHz, de los cuales 600 Hz serán producidos por las desintegraciones de <sup>40</sup>K. El resto de coincidencias se producen aleatoriamente.

- ➤ L2.- Para filtrar las coincidencias L1 aleatorias, se utiliza la orientación de los PMTs involucrados. Si los PMTs que han detectado un suceso L1 forman un ángulo mayor de 90° se considera una coincidencia aleatoria.

En base a esta definición de sucesos se elaboran otros filtros más complejos empleados en la reconstrucción de eventos físicos para discernir entre los eventos atmosféricos de fondo y los neutrinos cósmicos [27].

El diseño físico de la tarjeta CLB se describirá con más detalle en el capítulo 3, mientras que el sistema de adquisición *firmware* se describirá en el capítulo 6.

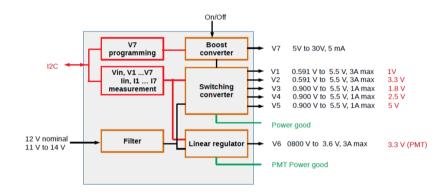

#### 2.2 Power Board

En la entrada de cada DOM hay un convertidor de tensión que se encarga de transformar la señal de alta tensión de 375-400 V DC proveniente del JB en una tensión de 12 V DC. La tarjeta electrónica denominada PB recibe esos 12 V y genera todas las tensiones que necesita el DOM: 1 V, 1,8 V, 2,5 V, dos alimentaciones de 3,3 V (una para la CLB y otra para la alimentación de los PMTs), 5 V y una tensión ajustable entre 5-30 V para el *Nanobeacon* [28]. Si todas las

tensiones, exceptuando la del *Nanobeacon* se han generado correctamente se activa una señal denominada *Power Good*.

Para generar la tensión del *Nanobeacon* se utilizan convertidores conmutados DC/DC y un convertidor *Boost*. La configuración del *Nanobeacon* se realiza desde la CLB mediante comunicación I<sup>2</sup>C (*Inter-Integrated Circuit*).

Mediante dos conversores analógicos/digital (*Analog to Digital Converter* – ADC) se permite leer todos los valores de tensión y corriente. La figura 2.2 muestra un esquema descriptivo de la PB con todas sus alimentaciones e interfaces de configuración.

**Figura 2.2.** Esquema de la tarjeta *Power Board*. A partir de una tensión de entrada de 12 V, se generan todas las tensiones necesarias para el funcionamiento del DOM. La PB permite configurar de forma remota la tensión del *Nanobeacon*, así como leer las tensiones y las corrientes de todas las alimentaciones. Figura adaptada de [25].

Para la correcta elección de los convertidores de tensión se hizo un estudio previo de la corriente necesaria para cada una de las alimentaciones. Esto permitió optimizar la eficiencia de la tarjeta. La tabla 2.1 muestra la relación de tensiones, corrientes y el modelo de regulador elegido para cada alimentación. El consumo total de un DOM es, aproximadamente, 6 W.

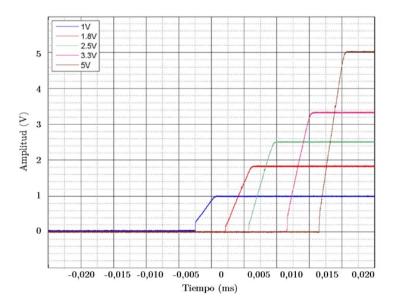

La PB lleva implícito un arranque secuencial de las tensiones que permite alimentar de forma correcta la FPGA. Esto evita que se generen corrientes excesivas durante el arranque que puedan dañar el sistema. La figura 2.3 muestra una imagen temporal del arranque secuencial de las alimentaciones de la PB.

| Tensión (V) | Corriente (A) | Eficiencia (%) | Modelo  |

|-------------|---------------|----------------|---------|

| 1           | 0,8           | 80             | OKL-T3  |

| 1,8         | 0,46          | 80             | OKL-T1  |

| 2,5         | 0,13          | 78             | LTM8022 |

| 3,3 (CLB)   | 0,33          | 90             | OKL-T1  |

| 3,3 (PMTs)  | 0,34          | 90             | OKL-T1  |

| 5           | 0,1           | 90             | MAX1754 |

**Tabla 2.1.** Principales tensiones generadas por la PB junto con los modelos de convertidor elegido en función de la eficiencia.

**Figura 2.3.** Secuencia de arranque de las tensiones de la PB. Imagen adaptada de [25].

Debido a la geometría del DOM, la PB debe ser una tarjeta circular de 13 cm de diámetro, donde sus componentes únicamente pueden estar situados en una capa. La figura 2.4 muestra una de las tarjetas electrónicas PB instalada en los módulos ópticos de KM3NeT.

**Figura 2.4.** Imagen de la tarjeta  $Power\ Board$  utilizada en la Fase 1 de KM3NeT.

# 2.3 Bases de los fotomultiplicadores

Las tarjetas electrónicas de las bases de los PMTs se encargan de generar la señal de alta tensión de alimentación y de digitalizar las señales analógicas que emiten.

La tensión de alimentación se genera mediante un elevador de tensión Cockroft Walton [29]. Los PMTs se alimentan de forma individual y su tensión de alimentación se puede configurar de forma remota vía I<sup>2</sup>C. El rango de alimentación es de -800 V a -1400 V. Esto permite ajustar la ganancia de cada PMT por separado.

La base de los PMTs incorpora dos chips Application Specific Integrated Circuit (ASIC). Uno de ellos, llamado PROMiS realiza la lectura de la

señal del PMT y el otro, denominado CoCo controla el circuito Cockroft-Walton.

El ASIC PROMiS incluye una etapa de pre-amplificación para incrementar la amplitud de la señal generada por el PMT, así como un comparador que genera una señal diferencial Low Voltage Differential Signal (LVDS) cuya anchura temporal se corresponde con el tiempo que la señal del PMT está por encima de un determinado valor umbral. Dicho tiempo se denomina Time over Threshold (ToT). El valor umbral es configurado remotamente mediante I<sup>2</sup>C. El ASIC PROMiS también permite habilitar o deshabilitar la señal de alta tensión, así como monitorizar las señales del PMT.

Por su parte, el ASIC CoCo se encarga de gestionar el circuito Cockroft-Walton para elevar de forma estable la tensión de los dínodos estableciendo una ganancia adecuada para cada PMT. Mediante este ASIC se establecen ganancias para los PMTs del orden de  $10^6$  para conseguir ToTs de 26-27 ns por fotoelectrón. La figura 2.5 muestra la imagen de un PMT junto con la tarjeta electrónica de su base.

Figura 2.5. Tarjeta electrónica de la base de los PMTs. Imagen obtenida de [25].

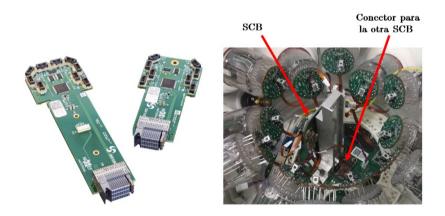

### 2.4 Signal Collector Board

Las señales LVDS que generan las bases de los PMTs se envían a la CLB mediante las tarjetas SCB. Una, denominada SCB\_Large, enviará a la CLB las señales de 19 PMTs, correspondientes a los PMTs situados en el hemisferio inferior del DOM, y la otra, denominada SCB\_Small, enviará las señales de los 12 PMTs situados en el hemisferio superior del DOM. Las SCBs también son las encargadas de enviar a los PMTs los comandos de configuración y monitorización que genera la CLB.

Las SCBs están compuestas por: un conector Molex 754332104 con el que se conectan a la CLB, un chip Complex Programmable Logic Device (CPLD) modelo Coolrunner de Xilinx para controlar y monitorizar las bases de los PMTs a través de la lectura de sensores de corriente, limitadores de corriente, un multiplexor para las diferentes líneas de I<sup>2</sup>C y un enlace que permite comunicar el sensor acústico con la CLB. La figura 2.6 muestra una imagen de las dos tarjetas SCB, junto con una vista del DOM donde se puede ver una SCB conectada y el hueco donde se conecta la otra SCB.

Figura 2.6. En esta figura se muestran las dos SCBs que se utilizan para conectar los 31 PMTs y el sensor acústico con la CLB (izquierda). Se muestra también un DOM abierto con una SCB conectada y se indica el lugar donde debe ir conectada la otra SCB (derecha). Imagen adaptada de [25].

### 2.5 Nanobeacon

Todos los DOMs de KM3NeT llevan incorporado un pequeño dispositivo de calibración denominado *Nanobeacon*. Con este dispositivo se puede controlar el desfase temporal entre DOMs de la misma DU, verificando *in situ* el sincronismo del sistema que se describirá con detalle en el capítulo 4.

El Nanobeacon consiste en una tarjeta electrónica que incorpora un diodo LED modelo HLMP-CB1A-XY0DD apuntando hacia arriba capaz de emitir pulsos cortos de luz, con flancos de subida < 3 ns y con intensidad suficiente para iluminar los DOMs de la misma DU situados por encima de él. Se ha demostrado que con la intensidad del LED y su ángulo de apertura sería posible incluso iluminar DUs adyacentes para calibrar sus desfases temporales. La tabla 2.2 muestra las principales características del diodo LED.

| Atributo               | Valor                |

|------------------------|----------------------|

| Longitud de onda       | 470  nm              |

| Ángulo de apertura     | 15°                  |

| Intensidad             | $12000 \mathrm{mcd}$ |

| Tamaño del encapsulado | T-1 ¾(5 mm)          |

**Tabla 2.2.** Principales características del diodo LED incorporado en la tarjeta *Nanobeacon*.

El diseño de la tarjeta electrónica está basado en el circuito ideado por J.S. Kapustinsky [30] capaz de emitir pulsos ultracortos mediante la descarga de un condensador a través de dos transistores de gran ancho de banda.

La señal de descarga de los condensadores es generada por la CLB y enviada mediante un cable trenzado de 25 cm de longitud al *Nanobeacon*. Todos los parámetros de esta señal se pueden configurar mediante la CLB, desde el número de pulsos, hasta su frecuencia [31].

Por el mismo cable trenzado se envía también la tensión a la que se carga el condensador del circuito. La señal de tensión se genera en la PB mediante un convertidor DC/DC modelo LT3464 y un convertidor digital-analógico (*Digital to Analog Converter* – DAC) conectado a la entrada de control del convertidor. El nivel de tensión se puede ajustar de forma remota mediante comunicación I<sup>2</sup>C. La CLB configura de forma adecuada la tensión de salida del DAC para que el LT3464 genere la tensión deseada para operar con el *Nanobeacon*.

Esta tarjeta electrónica proporciona un sistema de calibración de bajo coste, pocos elementos, gran fiabilidad y bajo consumo. El consumo del *Nanobeacon* durante las operaciones de calibración no excede de 0,1 W. Además, dado su bajo coste es factible instalar uno en cada DOM, lo cual otorga mucha redundancia y un aumento considerable de la fiabilidad global. La figura 2.7 muestra una imagen de la tarjeta electrónica.

Figura 2.7. Tarjeta Nanobeacon instalada en todos los DOMs de KM3NeT.

### 3 CENTRAL LOGIC BOARD

La CLB es el elemento principal del sistema de adquisición del experimento KM3NeT. Se trata de la tarjeta electrónica encargada de adquirir datos, gestionar la instrumentación y controlar el sincronismo. Los DOMs, y por ende la CLB de cada DOM, constituyen los nodos esclavos de la red óptica de KM3NeT que se describirá en el capítulo 4.

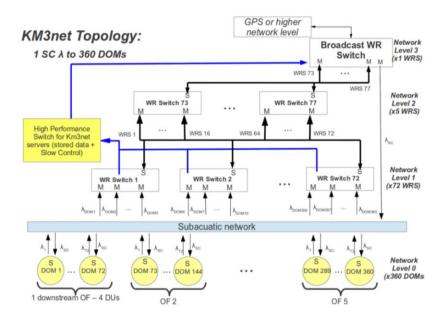

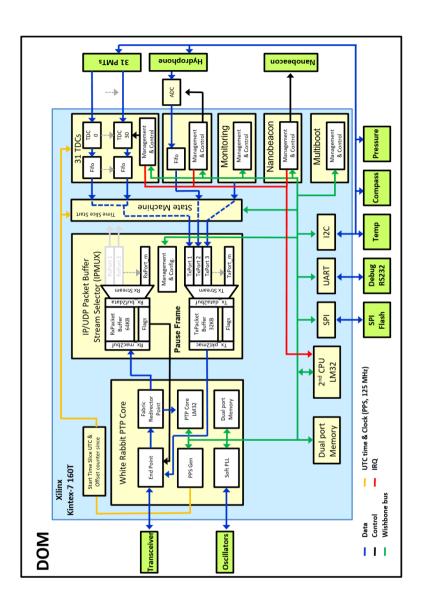

KM3NeT es una infraestructura que se está desarrollando en varias fases. En primera instancia, en la denominada Fase 1, se diseñó una estructura de red óptica basada en el protocolo WR [32], pero adaptada al gran volumen de KM3NeT para intentar reducir el uso de componentes electrónicos en el fondo del mar. Esta modificación tenía profundas implicaciones como la necesidad de incluir enlaces ópticos de larga distancia para los DOMs o la calibración previa de todos los DOMs antes de instalarlos en el fondo del mar. Pese al éxito en el desarrollo e implementación de esta topología, se vieron algunas vulnerabilidades, como la dificultad que representa el continuo mantenimiento y adaptación del protocolo WR o la calibración previa que hay que llevar a cabo de todos y cada uno de los módulos ópticos. Esto dio lugar a que se planteara un cambio de topología para la siguiente fase del experimento, la Fase 2.

La nueva topología de red de la Fase 2 estará basada en el protocolo WR estándar, sin modificaciones, lo cual implica tener que introducir conmutadores de red en el fondo del mar, pero, por otro lado, ya no se necesitan transceptores de larga distancia en la CLB. La evolución de las diferentes topologías de red será descrita con más precisión y más detalle en el capítulo 4.

## 3.1 Especificaciones de la tarjeta CLB

Las funcionalidades y requisitos que debe cumplir la tarjeta CLB son las siguientes:

- Adquisición de las señales de los PMTs mediante 31 canales denominados TDCs (*Time to Digital Converters*) con una resolución de 1 ns.

- > Adquisición de las señales del dispositivo piezoeléctrico del sistema de posicionamiento.

- > Implementación y control de los sensores de instrumentación: acelerómetro, giróscopo, brújula, sensor de presión, sensor de humedad y sensores de temperatura.

- > Esquemas de reloj de bajo ruido para permitir un sincronismo preciso.

- Un transceptor óptico de alta fiabilidad mediante el cual, se implementará un enlace de comunicación de 1,25 Gbps para gestionar el sincronismo y enviar los datos a la estación de la costa.

- ➤ Dos memorias Serial Peripheral Interface (SPI) FLASH de 256 Mb. Una de ellas servirá para almacenar las distintas imágenes firmware del sistema y proporcionar un modo seguro de arranque. La función de la otra memoria será almacenar estados y variables del software de control, concretamente de la memoria del microprocesador empotrado LM32 de Lattice Semiconductor.

- > Conectores para el envío de las señales de los PMTs. Los PMTs están conectados a unas tarjetas electrónicas que digitalizan la señal y la envían en formato diferencial LVDS.

- Para controlar la instrumentación, las memorias, y proporcionar medios para realizar pruebas, se deben incluir interfaces de comunicación USB, I<sup>2</sup>C, SPI y GPIO.

➤ Por último, se necesitará incluir una expansión para tarjetas FMC (FPGA Mezzanine Card) ya que en las bases de las DUs habrá una CLB que controlará diferentes elementos como amplificadores ópticos, láser, instrumentación, etc. Todos estos elementos estarán conectados a una tarjeta electrónica que se acoplará mediante conectores FMC a la CLB para su control.

## 3.2 Componentes principales de la CLB

Para cumplir con todas las especificaciones descritas en el apartado 3.1, se han seleccionado los siguientes componentes para realizar el diseño de la tarjeta electrónica.

### 3.2.1 Field Programmable Gate Array

El elemento principal de la CLB y el encargado de gestionar todas sus funcionalidades será una FPGA. Para elegir el modelo adecuado se han tenido en cuenta los requisitos técnicos que había que cumplir, así como un compromiso con el precio debido al gran número de FPGAs que se necesitan para la construcción del experimento. Como se verá con más detalle en el capítulo 6, para implementar los 31 TDCs con una resolución de 1 ns, se necesitarán 100 bloques de memoria de 36 Kb. La lógica estará formada por 31 bloques trabajando a una frecuencia de 250 MHz. En cuanto a la comunicación, únicamente se necesita un enlace a 1,25 Gbps, el cual servirá para el envío de datos y para intercambiar paquetes que permitan sincronizar el sistema.

Para la elección de la FPGA, teniendo en cuenta el precio y las prestaciones, se propusieron dos opciones de la serie 7 de Xilinx: Artix y Kintex. En base a una estimación previa de requisitos (lógica, memoria y velocidad) los modelos específicos a comparar fueron Kintex-7 XC7K160T (speed grade -2) y Artix-7 XC7A200T (speed grade -3) [33]. El término speed grade es un indicador del rendimiento de la FPGA. Un valor absoluto mayor dentro de una misma familia indica un mayor

rendimiento. La tabla 3.1 muestra una comparativa de ambas FPGAs con los bloques más importantes para la implementación del sistema de adquisición de KM3NeT.

|                       | Kintex-7 160T   | Artix-7 200T |

|-----------------------|-----------------|--------------|

| Celdas lógicas        | 162240          | 215360       |

| Block RAM 36 Kb       | 325             | 365          |

| RD/WR FIFO (ns)       | $0,\!36/0,\!39$ | 0,43/0,46    |

| Toggle Freq.(MHz)     | 1818            | 1412         |

| Entrada/salida        | 400             | 400          |

| Coste (>500 unidades) | 152 €/u         | 149 €/u      |

**Tabla 3.1.** Comparativa de prestaciones y coste para los modelos Artix-7 XC7A200T (*speed grade -3*) y Kintex-7 XC7K160T (*speed grade -2*).

La denominada frecuencia toggle es una métrica sobre la tecnología y el diseño de los componentes activos que indica la máxima frecuencia de reloj a la que puede funcionar [34]. Realmente este parámetro no indica la frecuencia máxima a la que puede conmutar la lógica, ya que depende de muchos otros factores como rutas, elementos lógicos utilizados, etc. Además, hasta que el diseño del firmware no está implementado no se puede saber con exactitud dicha frecuencia, pero sí que es útil para establecer que el modelo de Kintex es mucho más rápido que el de Artix. La frecuencia de toggle es un 30% más rápida y las lecturas/escrituras en memoria FIFO (First In First Out) son un 18% más rápidas [35, 36]. Las celdas lógicas que presenta el modelo Kintex serían suficientes para integrar todo el sistema de adquisición y sincronismo. Ambos modelos presentan, aproximadamente, los mismos bloques de memoria RAM y el mismo número de conexiones de entrada/salida y tampoco hay diferencia significativa en el precio. Por todo ello, el modelo seleccionado para la tarjeta CLB fue la Kintex-7 XC7K160 FBG676 (speed grade -2).

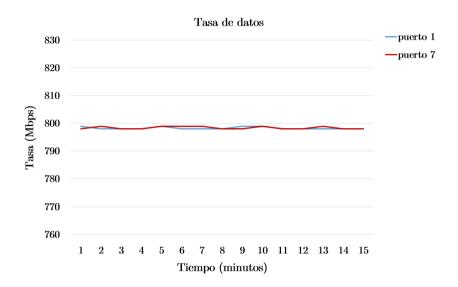

### 3.2.2 Transceptor óptico

Otro elemento importante de KM3NeT son los transceptores ópticos pues son los encargados de comunicar la CLB, mediante fibra óptica, con la estación de la costa. Su misión es enviar todo el tráfico de datos y gestionar el sincronismo de los módulos ópticos. La tasa de datos esperada en el experimento y la capacidad de los conmutadores que forman la red óptica de KM3NeT no requieren mucho ancho de banda por lo que 1,25 Gbps es suficiente. Las principales características que debe cumplir el transceptor óptico son:

- Tasa de datos de 1,25 Gbps.

- Comunicación dual.

- > Aptos para entornos hostiles.

- Alta fiabilidad, ya que deberán estar funcionando muchos años en el interior de los DOMs sin la posibilidad de ser reemplazados.

- Al tratarse de un periodo largo de producción, se debe evitar la obsolescencia.

Con estos requisitos se seleccionaron dos modelos, uno de la compañía Glenair Inc. y otro de Cotsworks LLC. La tabla 3.2 muestra las principales características de ambos.

|                   | Glenair<br>057-231 | Cotsworks<br>SFB-G53 |

|-------------------|--------------------|----------------------|

| Interfaz SFF-8742 | Sí                 | Sí                   |

| Conector óptico   | GC                 | $_{ m LC}$           |

| Consumo (W)       | 0,87               | 1,13                 |

|                   | MIL-STD-810        |                      |

| Certificaciones   | Vibraciones        | MIL-STD-833          |

| Certificaciones   | MIL-STD-883        | Vibraciones          |

|                   | Descargas ESD      |                      |

**Tabla 3.2.** Comparativa de las principales características de los transceptores Glenair 057-231 y Cotsworks SFB-G53 [37].

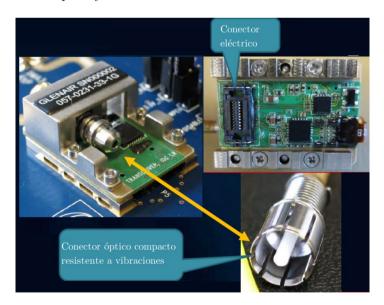

Ambos modelos cumplen con los requisitos básicos para su instalación en la CLB, aunque el consumo es significativamente menor en el modelo de Glenair. Los precios no aparecen en la tabla 3.2 debido a acuerdos de confidencialidad con las compañías, pero la diferencia no es significativa. Tanto el conector óptico como el eléctrico de Glenair son más robustos y más adecuados para entornos y procesos de instalación hostiles como KM3NeT. De hecho, este transceptor se utiliza principalmente para uso militar y aviónica dada su alta fiabilidad y robustez. Aunque ambos dispositivos presentan características similares, setransceptor de Glenair. La aplicación de este tipo de transceptores para uso militar le otorga más fiabilidad. También es importante saber que la compañía Glenair es una compañía familiar que adquiere un compromiso con el cliente ante este tipo de compras, asegurando que no se producirá obsolescencia, característica vital para experimentos como KM3NeT cuya construcción es de larga duración. La figura 3.1 muestra una imagen del modelo de transceptor de Glenair seleccionado junto con el conexionado óptico y eléctrico.

**Figura 3.1.** Modelo Glenair 057-0231 seleccionado para las CLBs de KM3NeT junto con su conexión óptica y eléctrica.

#### 3.2.3 Sistema de reloj

Para poder utilizar el protocolo de sincronismo WR en la CLB se necesita un sistema de reloj adecuado. Son necesarios dos relojes, uno de 125 MHz y otro de 124,992 MHz. Ambos relojes permitirán sincronizar la CLB con el nodo maestro. Para poder conseguir un sincronismo de gran precisión se necesitan relojes con bajo ruido de fase para que sus fluctuaciones influyan lo menos posible en la capacidad de sincronismo del sistema. Del reloj de 125 MHz se extraerá también el reloj principal de 62,5 MHz del sistema de adquisición.

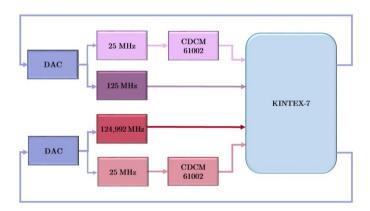

Para la elección de los relojes se han evaluado varios modelos y topologías. La figura 3.2 muestra el sistema de reloj implementado en la CLB donde se observan las dos formas de generar los relojes de 125 MHz y 124,992 MHz.

**Figura 3.2.** Esquema de reloj implementado en la CLB. Varios modelos y varias topologías han sido planteadas. El diseño de esta tarjeta permite la instalación de todos ellos para su evaluación.

Para generar los relojes de 125 MHz y 124,992 MHz se utilizan dos métodos. El primero de ellos consiste en poner un oscilador controlado por tensión (*Voltage Controlled Crystal Oscillator* – VCXO) de la frecuencia correspondiente y conectarlo directamente a la FPGA. Para

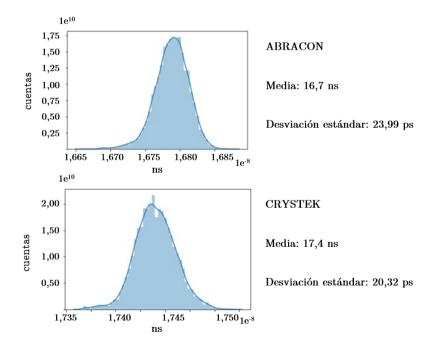

esta implementación existen varios modelos que pueden ser adecuados. Para la CLB se han seleccionado modelos de las compañías Crystek Crystals Corporation [38] y Abracon LLC [39]. La tabla 3.3 resume las principales características de ambos osciladores.

|                         | CRYSTEK<br>CVPD 922   | ABRACON<br>ABLNO      |

|-------------------------|-----------------------|-----------------------|

| Estándar de salida      | LVPECL                | LVCMOS                |

| Sensibilidad ajuste     | 25  ppm               | 40 ppm                |

| Ruido de fase (10 Hz)   | $-85~\mathrm{dBc/Hz}$ | $-70~\mathrm{dBc/Hz}$ |

| Degradación a 10 años   | 10 ppm                | 28 ppm                |

| Coste unitario (>500 u) | 38,5 \$/u             | 9,7 \$/u              |

**Tabla 3.3.** Comparativa entre las principales características de los osciladores de Crystek y Abracon.

En base a los datos recogidos en la tabla 3.3, Crystek presenta una mejor sensibilidad para ajustar la frecuencia del oscilador y tiene un menor ruido de fase, lo que se traduce en menores fluctuaciones (*jitter*) y mejor capacidad de sincronismo. Por otro lado, su precio es mucho más elevado.

Como ambos modelos pueden trabajar en la CLB, se optó por diseñar una tarjeta electrónica en la que se pudiesen montar ambos osciladores indistintamente. Ambos tienen el mismo número de conexiones y son del mismo tamaño. La principal diferencia es que el modelo de Crystek tiene un estándar lógico de salida diferencial y el de Abracon es no diferencial. Esto hace que sea necesario incorporar resistencias y condensadores para adecuar el estándar lógico en función del tipo de oscilador que se vaya a soldar. Al diseñarlo de esta manera es posible evaluar el rendimiento de los osciladores *in-situ* en los primeros prototipos de la CLB, ver cómo afectan a la capacidad de sincronismo y tomar así la mejor decisión sobre qué oscilador elegir.

El segundo método consiste en utilizar un oscilador de 25 MHz (modelo Kvocera KV7050) controlado por tensión v conectarlo a un sintetizador de frecuencias (CDCM 61002) para obtener la frecuencia deseada [40]. Este sistema presenta el problema de inducir más jitter y perder capacidad de sincronismo, pero por el contrario tiene la ventaja de estar formado por componentes comerciales con mayor disponibilidad y menor precio que Crystek o Abracon, ya que estos osciladores se fabrican expresamente a la frecuencia que se desea, lo que hace que su tiempo de entrega sea de varias semanas y su precio bastante más elevado. Desde el punto de vista del sincronismo, Crystek o Abracon son la mejor solución. Aun así, se ha incluido también el esquema de reloj basado en componentes comerciales como medida de seguridad dada la gran importancia del reloj. La CLB es un sistema aislado e inaccesible por lo que un fallo que produzca la pérdida del oscilador podría significar la pérdida entera del módulo óptico. Disponer de ambos esquemas de reloj no supone un aumento de complejidad ni de coste y proporciona una medida de respaldo ante la posibilidad de perder alguno de los relojes principales.

#### 3.2.4 Sensores de instrumentación

Se ha dotado a la CLB de diversos sensores de instrumentación, todos ellos controlados por interfaz I<sup>2</sup>C. Existen diferentes sensores encargados de controlar las condiciones ambientales de la CLB dentro del DOM, como son los sensores de temperatura, presión y humedad. Además, el DOM contiene otros sensores como el giróscopo, brújula o el acelerómetro encargados de monitorizar en todo momento la orientación y la posición exacta del DOM para tener en cuenta los desplazamientos producidos por las corrientes marinas de manera que no afecten a la reconstrucción de los eventos físicos. Las tablas 3.4 y 3.5 muestran los modelos de los sensores elegidos junto con sus principales características.

|             | Temperatura | Humedad       | Presión        |

|-------------|-------------|---------------|----------------|

| Modelo      | SH          | IT21          | LPS25HB        |

| Salida      | 12 bits     | 8 bits        | 24 bits        |

| Rango       | [-40,125]°  | [0,100] %H.R. | [260,1260] hPa |

| Encapsulado | DFN         |               | LGA            |

**Tabla 3.4.** Sensores elegidos para el control de las condiciones medioambientales internas del DOM junto con sus principales características.

|             | Acelerómetro        | Giróscopo                 | Brújula                         |

|-------------|---------------------|---------------------------|---------------------------------|

| Modelo      | LIS3LV02DL          | L3GD20H                   | LSM303AGR                       |

| Salida      | 16 bits             | 16 bits                   | 16 bits                         |

| Rango       | $Ac:\pm 2/\pm 6[g]$ | $[x]\pm 245 dps$          | $Ac:\pm 2/\pm 4/\pm 8\pm 16[g]$ |

|             | [x,y,z]             | $[y]\pm 500 dps$          | Mag: $\pm 50$ gauss             |

|             |                     | $[z]\pm2000~\mathrm{dps}$ |                                 |

| Encapsulado | $_{ m LGA}$         | $_{ m LGA}$               | $_{ m LGA}$                     |

**Tabla 3.5.** Principales sensores de instrumentación seleccionados para controlar el movimiento y posición de los DOMs durante su funcionamiento.

#### 3.2.5 Configuración de la CLB

La CLB se puede configurar bien enviando el archivo de configuración mediante la cadena de JTAG (Joint Test Action Group) o bien cargándolo desde una de las dos memorias Flash no volátiles [41]. Para este último caso, la FPGA Kintex-7 está conectada a una memoria Flash SPI de 256 Mb. El modelo seleccionado es S25FL256-S. Este modelo permite almacenar hasta cinco imágenes de configuración diferentes. En la CLB se almacenarán cuatro imágenes. Estas imágenes proporcionan la configuración inicial de la FPGA tras el establecimiento de las tensiones de alimentación. Remotamente se podrá acceder a la memoria para cambiar los archivos de configuración o para configurar la FPGA con cualquiera de los archivos almacenados. Se ha seleccionado una memoria SPI en vez de Byte Peripheral Interface (BPI) por la simplicidad de conexionado a pesar de que el tiempo de configuración de

la FPGA mediante SPI es mayor que mediante BPI, pero este no es un aspecto crítico para KM3NeT. La tabla 3.6 muestra el mapa de memoria de la S25FL256-S utilizada para la configuración y arranque del sistema.

| Desplazamiento | Tamaño     | Descripción |

|----------------|------------|-------------|

| 0x00000000     | 0x00800000 | Golden      |

| 0x00800000     | 0x00800000 | Imagen-1    |

| 0x01000000     | 0x00800000 | Imagen-2    |

| 0x01800000     | 0x00800000 | Imagen-3    |

**Tabla 3.6.** Mapa del direccionamiento de la memoria flash SPI S25FL256 utilizada para la configuración de la FPGA de la CLB. La memoria tiene capacidad para almacenar hasta cinco imágenes, pero cuatro son suficientes para KM3NeT.

Cuando se inicia la alimentación, la FPGA arranca con la imagen denominada Golden. Se trata de una imagen de configuración muy segura y estable que se utiliza para el arranque inicial o como imagen de seguridad en el caso de que alguna de las nuevas imágenes con las que se intente configurar la FPGA no tenga un funcionamiento adecuado o esté corrupta. La carga de una imagen no adecuada podría hacer que el módulo óptico se perdiese para siempre. La imagen Golden está en una zona de memoria protegida contra escritura para que no pueda sobrescribirse por error y únicamente configura la FPGA para tener acceso al diagnóstico y a la recuperación del sistema. Tras iniciar la imagen Golden, automáticamente se carga la Imagen-1, denominada Runtime, la cual contiene la imagen de configuración más reciente y estable del sistema. Las otras dos zonas de memoria se utilizan para almacenar imágenes anteriores o realizar pruebas con nuevas imágenes que aún no son estables.

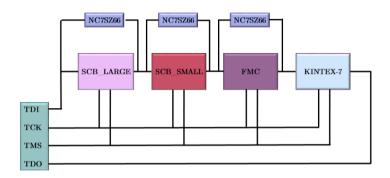

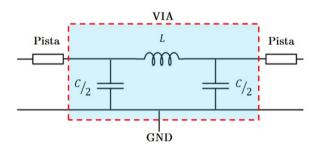

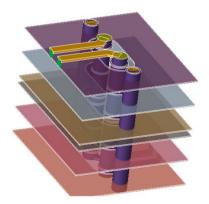

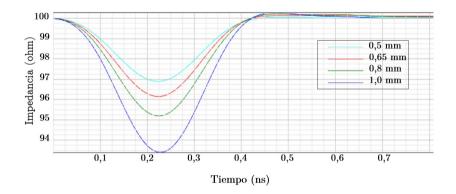

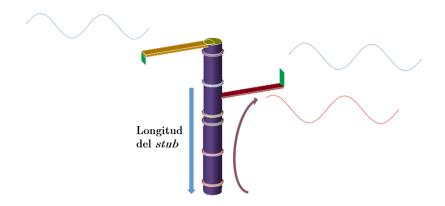

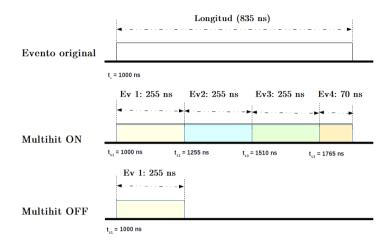

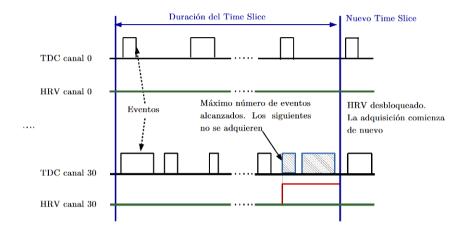

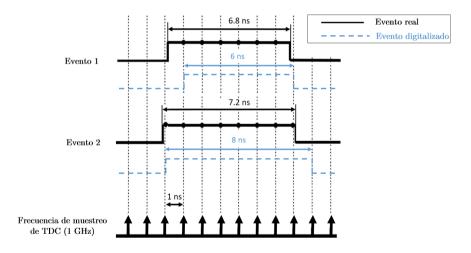

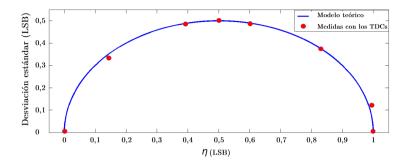

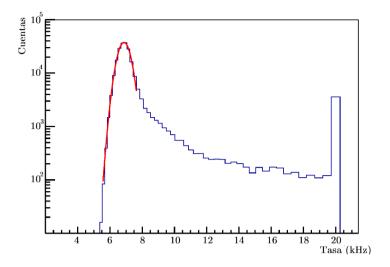

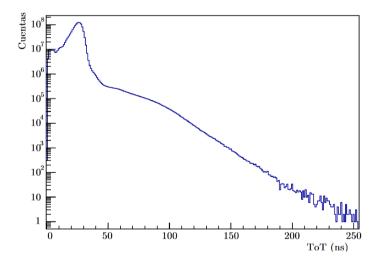

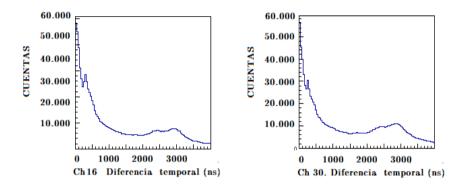

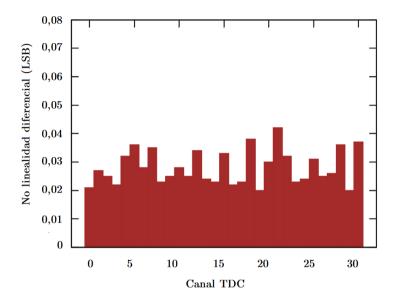

La otra forma de configurar la FPGA es mediante la cadena de JTAG. Además de la FPGA, las tarjetas electrónicas SCB\_Large y SCB\_Small, las cuales envían las señales de los fotomultiplicadores, y el conector FMC están conectadas a la cadena de JTAG. Si alguna de